© 2005 Ubicom, Inc. All rights reserved.

- 35 -

www.ubicom.com

SX20AC/SX28AC

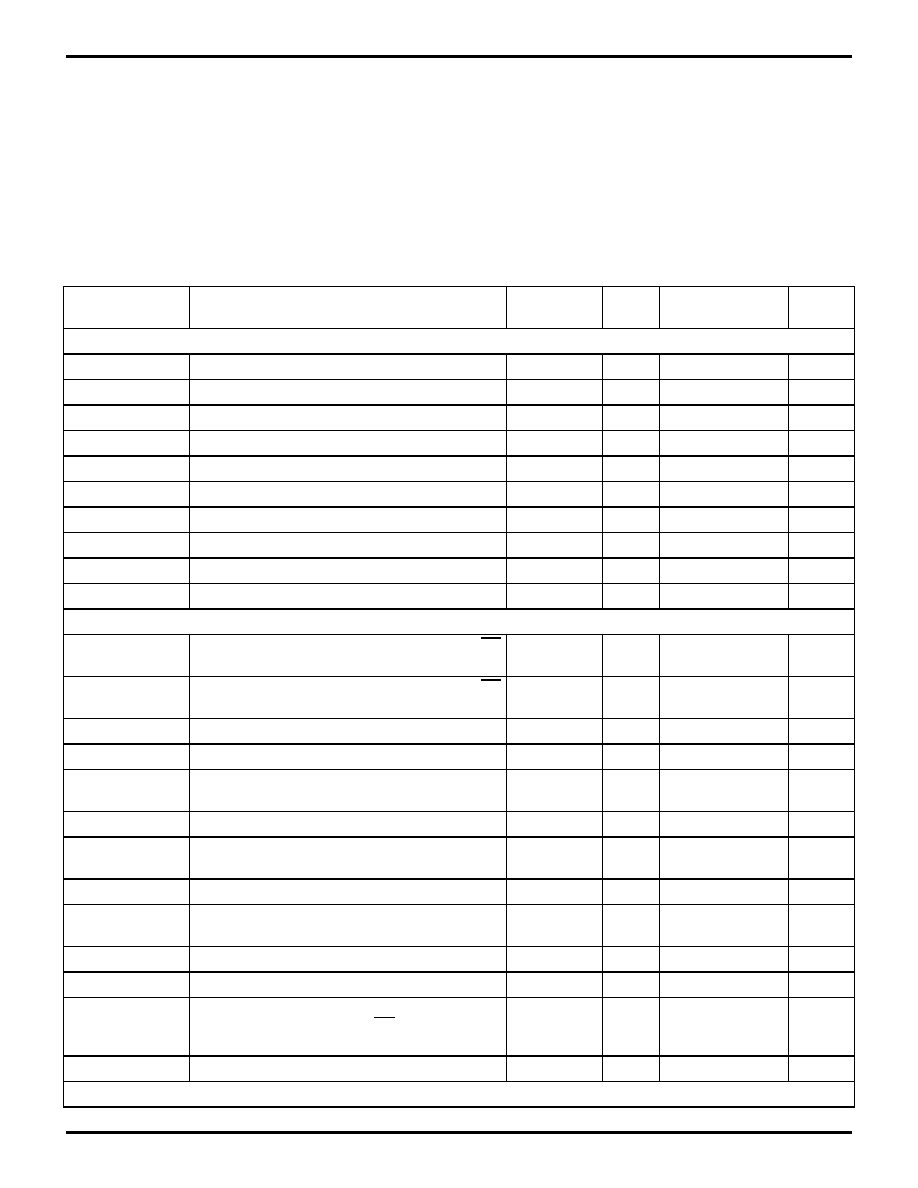

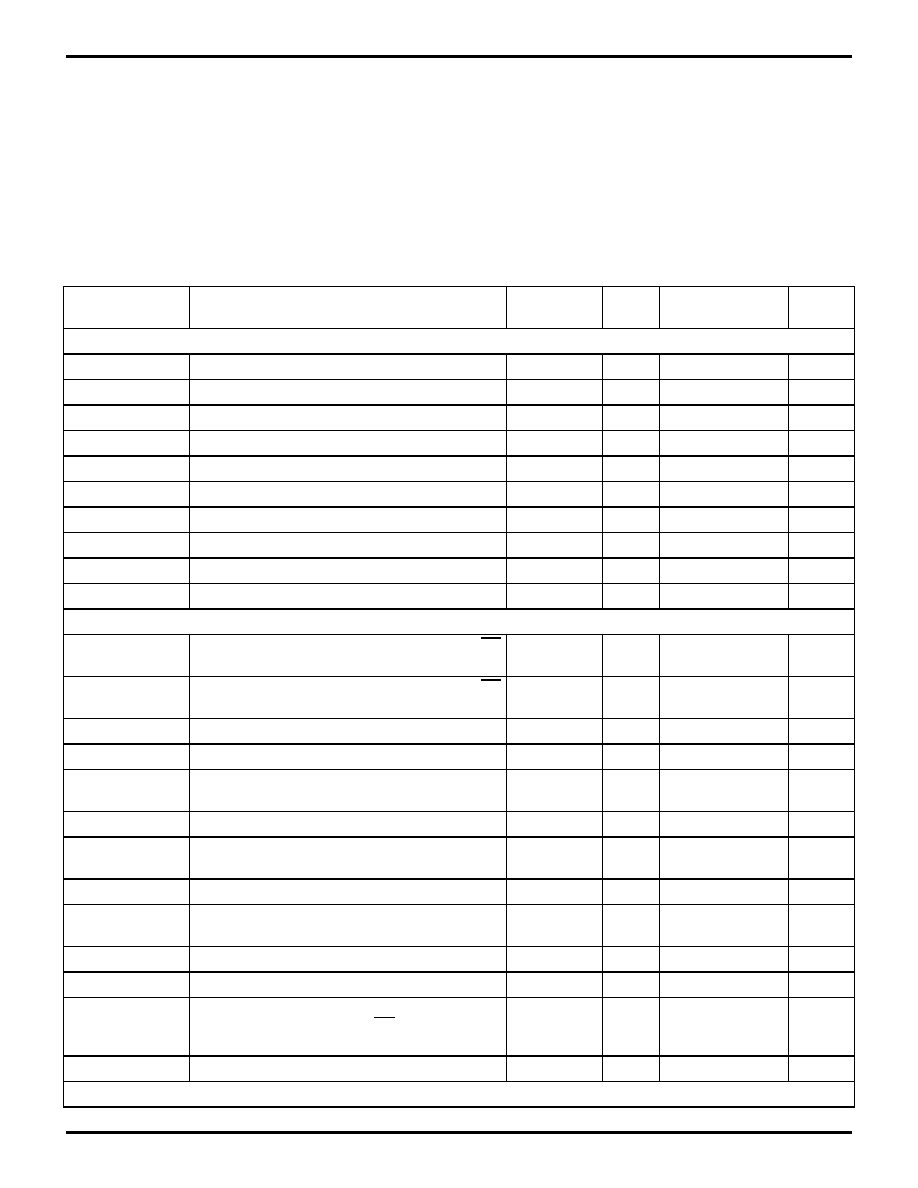

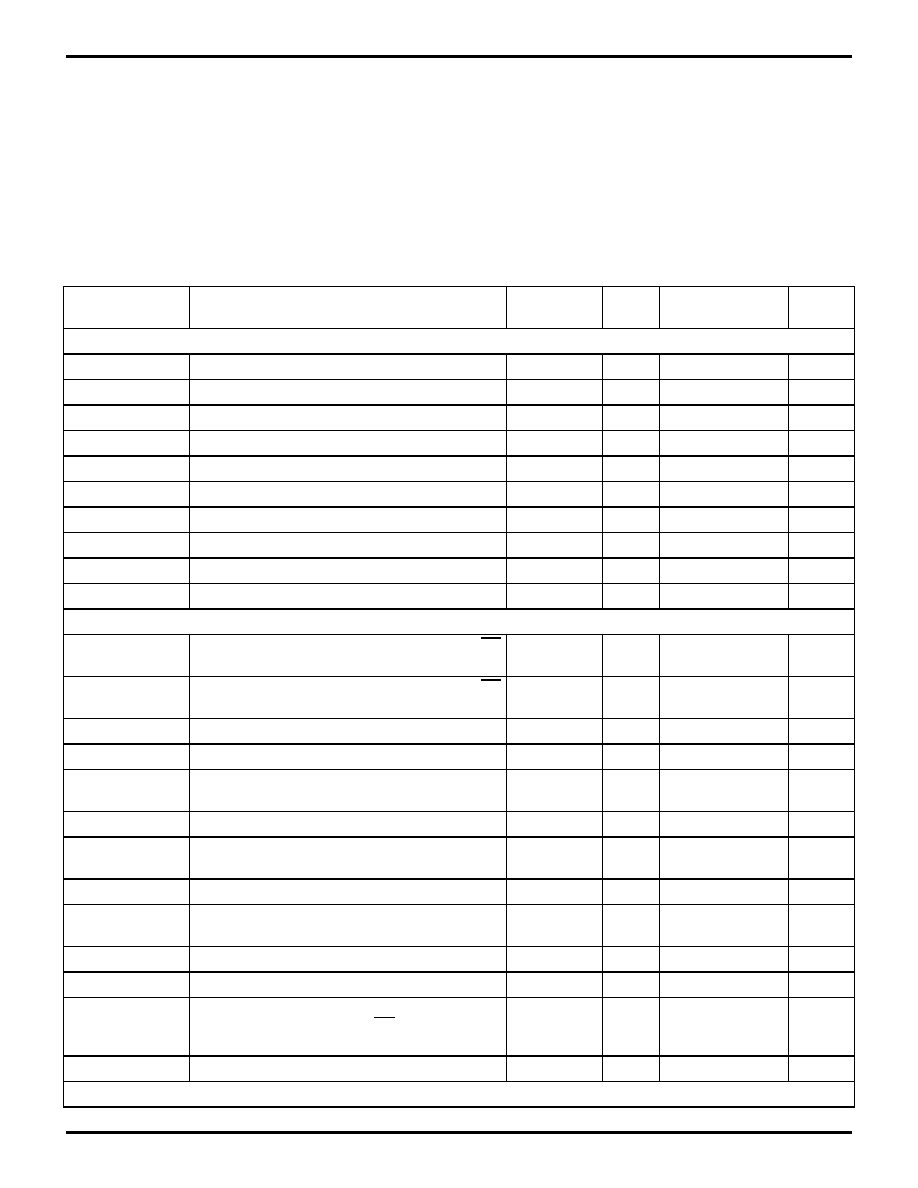

16.0 INSTRUCTION SET SUMMARY TABLE

Table 16-1 lists all of the instructions, organized by cate-

gory. For each instruction, the table shows the instruction

mnemonic (as written in assembly language), a brief

description of what the instruction does, the number of

instruction cycles required for execution, the binary

opcode, and the status bits affected by the instruction.

The "Cycles" column typically shows a value of 1, which

means that the overall throughput for the instruction is

one per clock cycle. In some cases, the exact number of

cycles depends on the outcome of the instruction (such

as the test-and-skip instructions) or the clocking mode

(Compatible or Turbo). In those cases, all possible num-

bers of cycles are shown in the table.

The instruction execution time is derived by dividing the

oscillator frequency by either one (Turbo mode) or four

(Compatible mode). The divide-by factor is selected

through the FUSE Word register.

Table 16-1. The SX Instruction Set

Mnemonic,

Operands

Description

Cycles

(Compatible)

Cycles

(Turbo)

Opcode

Bits

Affected

Logical Operations

AND fr, W

AND of fr and W into fr (fr = fr & W)

1

1

0001 011f ffff

Z

AND W, fr

AND of W and fr into W (W = W & fr)

1

1

0001 010f ffff

Z

AND W,#lit

AND of W and Literal into W (W = W & lit)

1

1

1110 kkkk kkkk

Z

NOT fr

Complement of fr into fr (fr = fr ^ FFh)

1

1

0010 011f ffff

Z

OR fr,W

OR of fr and W into fr (fr = fr | W)

1

1

0001 001f ffff

Z

OR W,fr

OR of W and fr into fr (W = W | fr)

1

1

0001 000f ffff

Z

OR W,#lit

OR of W and Literal into W (W = W | lit)

1

1

1101 kkkk kkkk

Z

XOR fr,W

XOR of fr and W into fr (fr = fr ^ W)

1

1

0001 101f ffff

Z

XOR W,fr

XOR of W and fr into W (W = W ^ fr)

1

1

0001 100f ffff

Z

XOR W,#lit

XOR of W and Literal into W (W = W ^ lit)

1

1

1111 kkkk kkkk

Z

Arithmetic and Shift Operations

ADD fr,W

Add W to fr (fr = fr + W); carry bit is added if CF

bit in FUSEX register is cleared to 0

1

1

0001 111f ffff

C, DC, Z

ADD W,fr

Add fr to W (W = W + fr); carry bit is added if CF

bit in FUSEX register is cleared to 0

1

1

0001 110f ffff

C, DC, Z

CLR fr

Clear fr (fr = 0)

1

1

0000 011f ffff

Z

CLR W

Clear W (W = 0)

1

1

0000 0100 0000

Z

CLR !WDT

Clear Watchdog Timer, clear prescaler if as-

signed to the Watchdog (TO = 1, PD = 1)

1

1

0000 0000 0100

TO, PD

DEC fr

Decrement fr (fr = fr - 1)

1

1

0000 111f ffff

Z

DECSZ fr

Decrement fr and Skip if Zero (fr = fr - 1 and skip

next instruction if result is zero)

1 or

2 (skip)

1 or

2 (skip)

0010 111f ffff

none

INC fr

Increment fr (fr = fr + 1)

1

1

0010 101f ffff

Z

INCSZ fr

Increment fr and Skip if Zero (fr = fr + 1 and skip

next instruction if result is zero)

1 or

2 (skip)

1 or

2 (skip)

0011 111f ffff

none

RL fr

Rotate fr Left through Carry (fr = << fr)

1

1

0011 011f ffff

C

RR fr

Rotate fr Right through Carry (fr = >> fr)

1

1

0011 001f ffff

C

SUB fr,W

Subtract W from fr (fr = fr - W); complement of

the carry bit is subtracted if CF bit in FUSEX

register is cleared to 0

1

1

0000 101f ffff

C, DC, Z

SWAP fr

Swap High/Low Nibbles of fr (fr = <> fr)

1

1

0011 101f ffff

none

Bitwise Operations