© 2005 Ubicom, Inc. All rights reserved.

- 29 -

www.ubicom.com

SX20AC/SX28AC

14.0 REGISTER STATES UPON

DIFFERENT RESET OPERATIONS

The effect of different reset operation on a register

depends on the register and the type of reset operation.

Some registers are initialized to specific values, some

are left unchanged, some are undefined, and some are

initialized to an unknown value.

A register that starts with an unknown value should be

initialized by the software to a known value; you cannot

simply test the initial state and rely on it starting in that

state consistently.

Table 14-1 lists the SX registers and shows the state of

each register upon different reset.

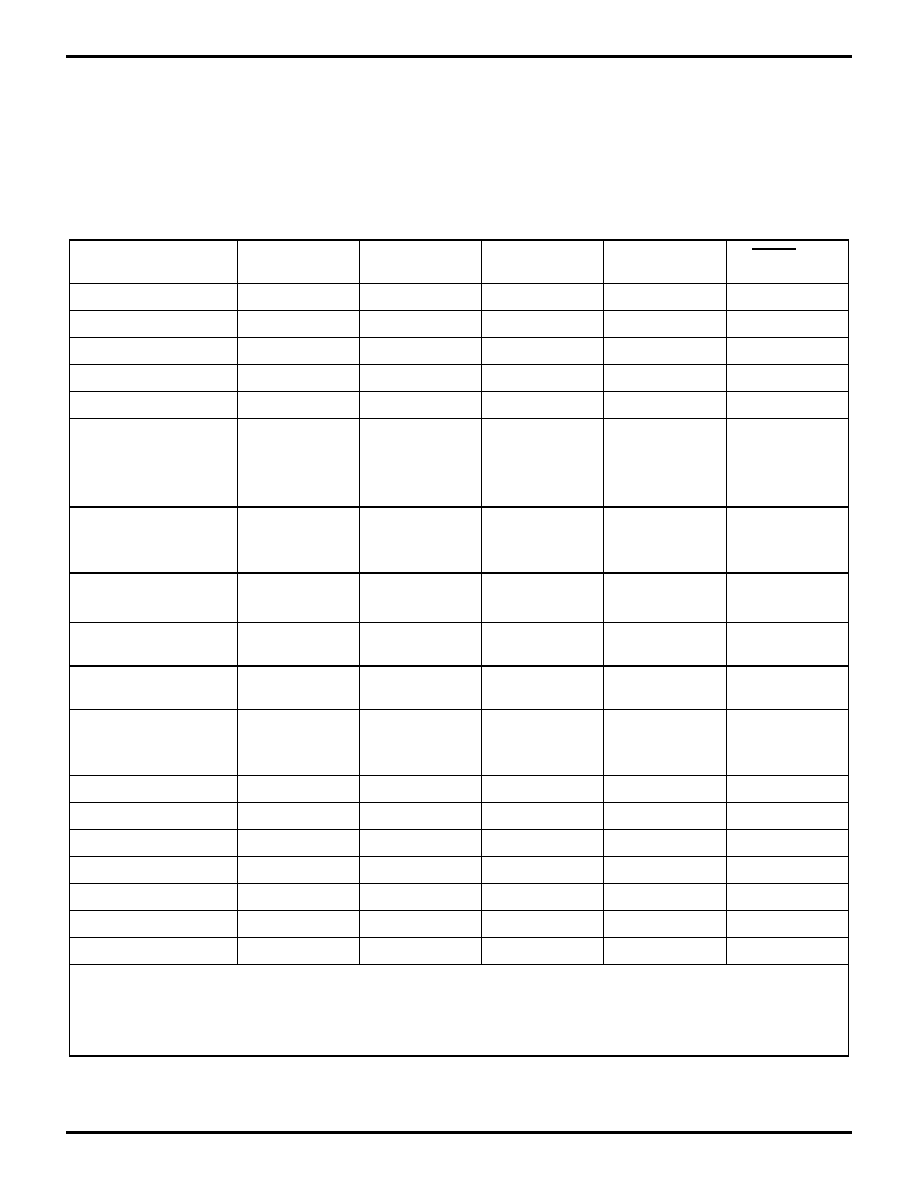

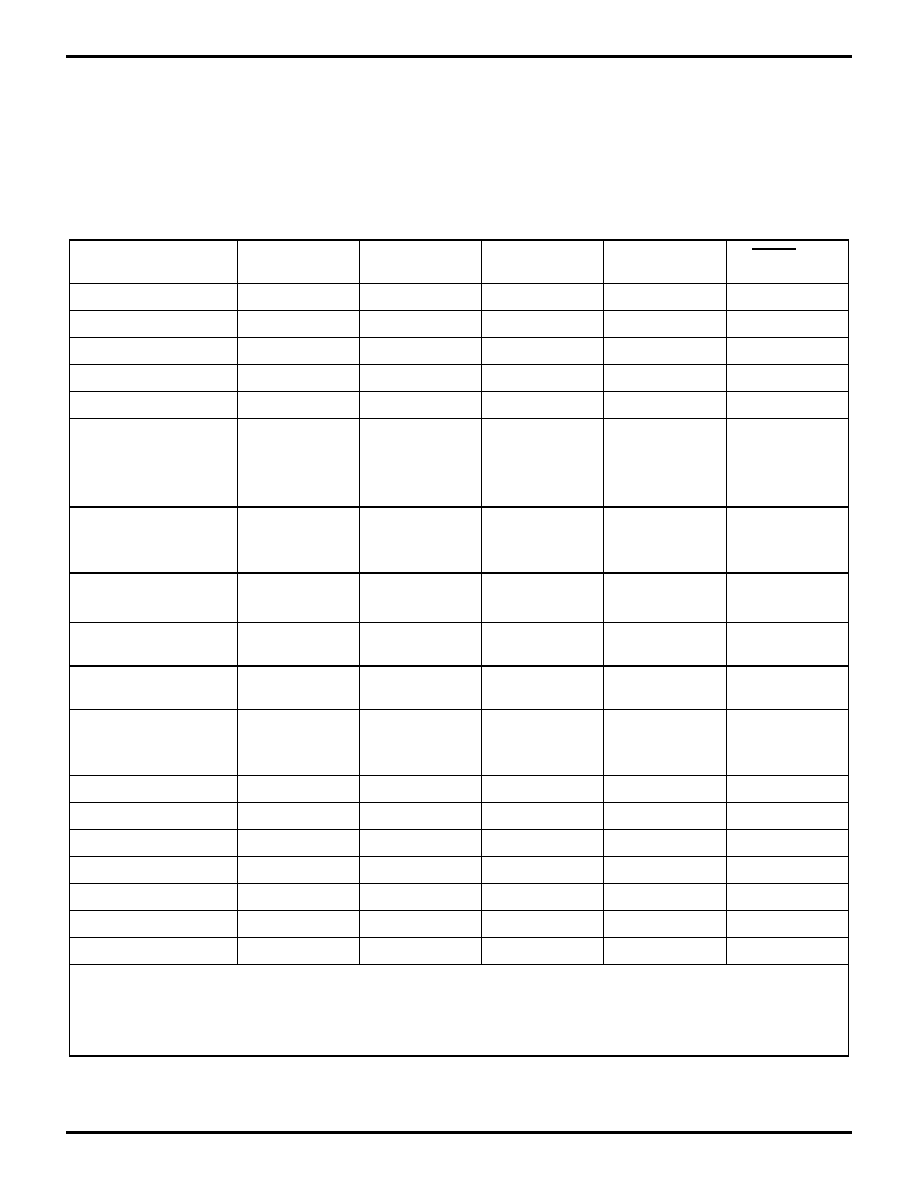

Table 14-1. Register States Upon Different Resets

Register

Power-On

Wakeup

Brown-out

Watchdog

Timeout

MCLR pin

W

Undefined

Unchanged

Undefined

Unchanged

Unchanged

OPTION

FFh

FFh

FFh

FFh

FFh

MODE

0Fh

0Fh

0Fh

0Fh

0Fh

RTCC (01h)

Undefined

Unchanged

Undefined

Unchanged

Unchanged

PC (02h)

FFh

FFh

FFh

FFh

FFh

STATUS (03h)

Bits 0-2: Unde-

fined

Bits 3-4: 11

Bits 5-7: 000

Bits 0-2: Un-

changed.

Bits 3-4: Unch.

Bits 5-7: 000

Bits 0-4: Unde-

fined

Bits 5-7: 000

Bits 0-2: Un-

changed

Bits 3-4: (Note 1)

Bits 5-7: 000

Bits 0-2: Un-

changed

Bits 3-4: (Note 2)

Bits 5-7: 000

FSR (04h)

Undefined

Bits 0-6: Un-

changed

Bit 7: 1

Bits 0-6: Unde-

fined

Bit 7: 1

Bits 0-6: Un-

changed

Bit 7: 1

Bits 0-6: Un-

changed

Bit 7: 1

RA/RB/RC

Direction

FFh

FFh

FFh

FFh

FFh

RA/RB/RC Data

(05/06/07h)

Undefined

Unchanged

Undefined

Unchanged

Unchanged

Other File Registers -

SRAM

Undefined

Unchanged

Undefined

Unchanged

Unchanged

CMP_B

Bits 0, 6-7: 1

Bits 1-5: Unde-

fined

Bits 0, 6-7: 1

Bits 1-5: Unde-

fined

Bits 0, 6-7: 1

Bits 1-5: Unde-

fined

Bits 0, 6-7: 1

Bits 1-5: Unde-

fined

Bits 0, 6-7: 1

Bits 1-5: Unde-

fined

WKPND_B

Undefined

Unchanged

Undefined

Unchanged

Unchanged

WKED_B

FFh

FFh

FFh

FFh

FFh

WKEN_B

FFh

FFh

FFh

FFh

FFh

ST_B/ST_C

FFh

FFh

FFh

FFh

FFh

LVL_A/LVL_B/LVL_C

FFh

FFh

FFh

FFh

FFh

PLP_A/PLP_B/PLP_C

FFh

FFh

FFh

FFh

FFh

Watchdog Counter

Undefined

Unchanged

Undefined

Unchanged

Unchanged

NOTE: 1. Watchdog reset during power down mode: 00 (TO, PD)

Watchdog reset during Active mode: 01 (TO, PD)

NOTE: 2. External reset during power down mode: 10 (TO, PD)

External reset during Active mode: Unchanged (TO, PD). Debug Tool may clear PD.