© 2005 Ubicom, Inc. All rights reserved.

- 28 -

www.ubicom.com

SX20AC/SX28AC

sequence where the MCLR and V

dd

pins are tied

together. The V

dd

signal is stable before the DRT time-

out period expires. In this case, the device will receive a

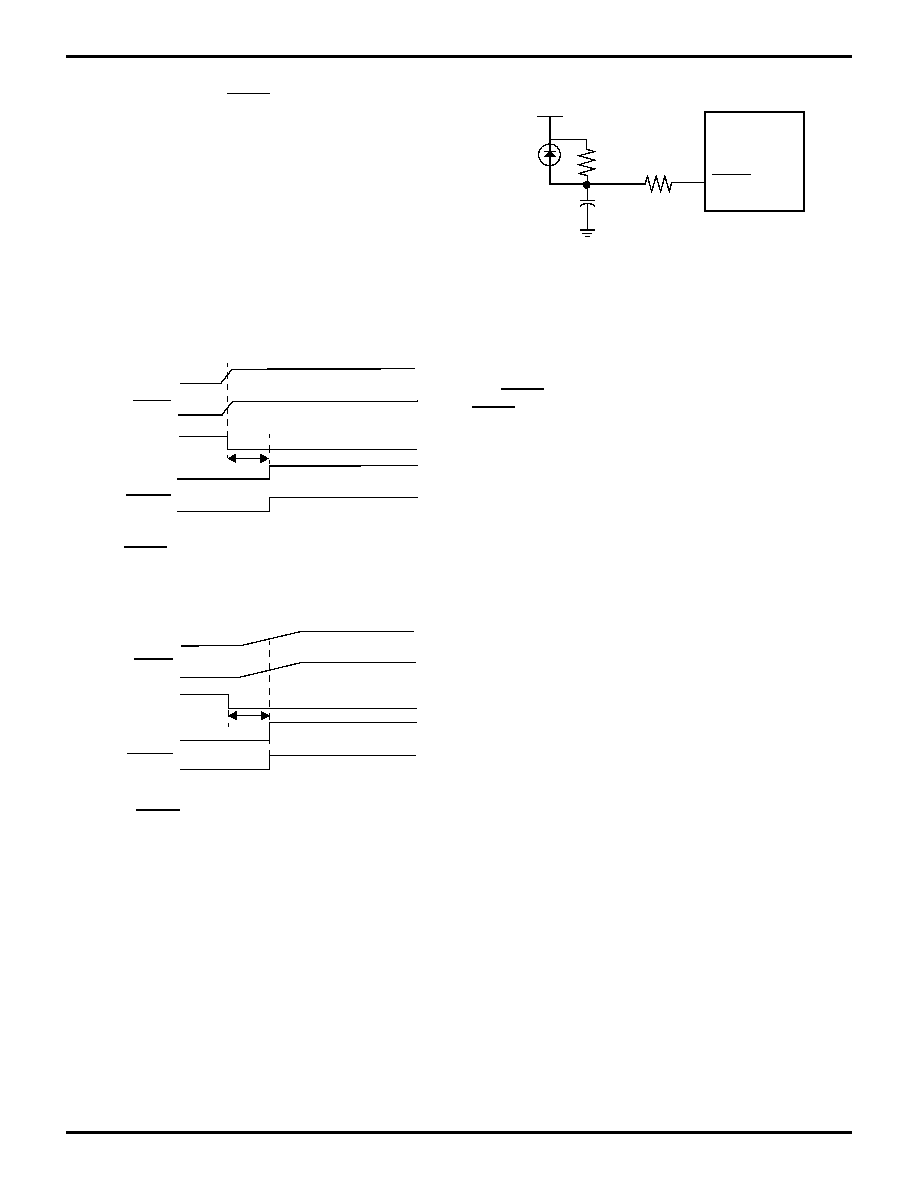

where V

dd

rises too slowly. In this scenario, the DRT will

time-out prior to V

dd

reaching a valid operating voltage

level (V

dd

min). This means the device will come out of

reset and start operating with the supply voltage not at a

valid level. In this situation, it is recommended that you

delay should exceed the time period it takes V

dd

to reach

a valid operating voltage.

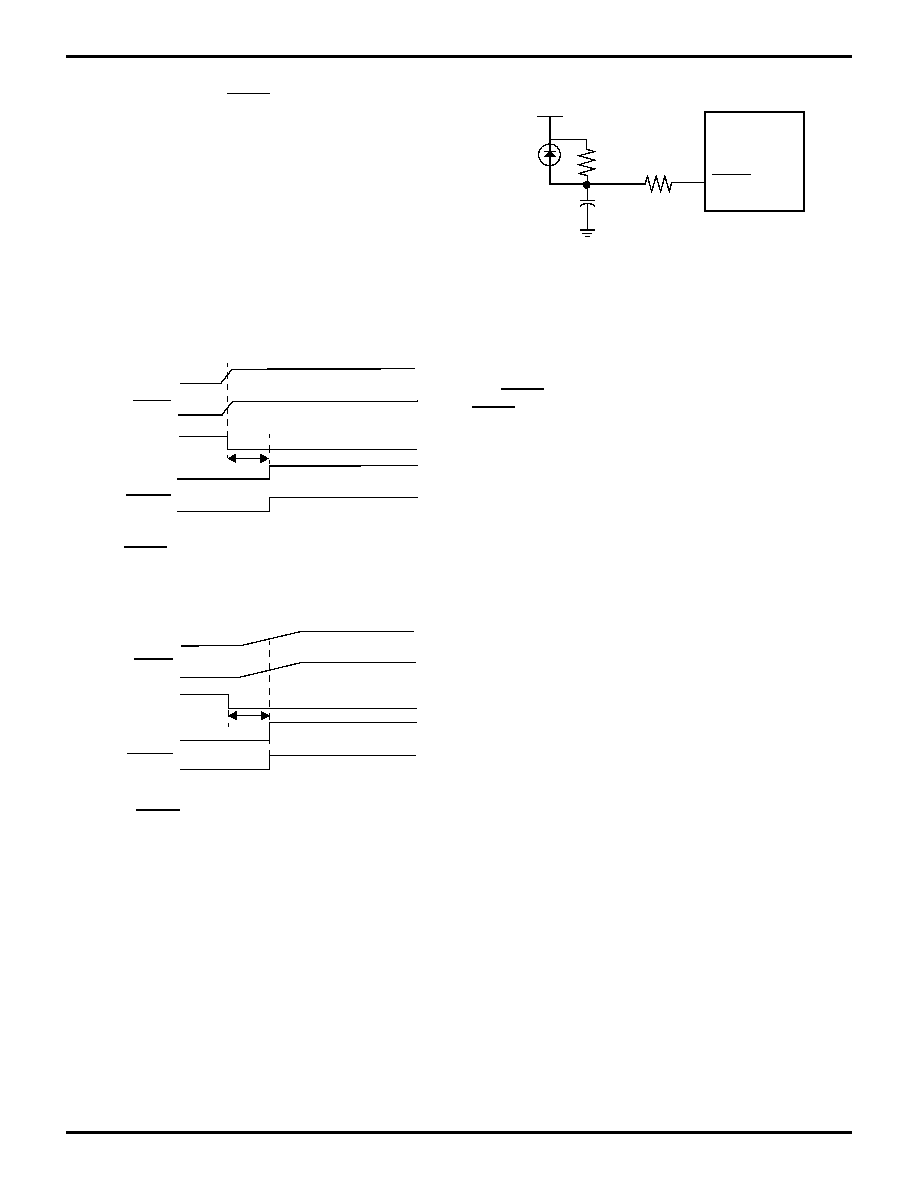

Note 1: The external Power-On Reset circuit is required

only if V

dd

power-up is too slow. The diode D helps dis-

charge the capacitor quickly when V

dd

powers down.

Note 2: R < 40 k

is recommended to make sure that

voltage drop across R does not violate the device electri-

cal specifications.

Note 3: R1 = 100

to 1k will limit any current flowing

into MCLR from external capacitor C. This helps prevent

MCLR pin breakdown due to Electrostatic Discharge

(ESD) or Electrical Overstress (EOS).

13.0 BROWN-OUT DETECTOR

The on-chip brown-out detection circuitry resets the

device when V

dd

dips below the specified brown-out volt-

age. The device is held in reset as long as V

dd

stays

below the brown-out voltage. The device will come out of

reset when V

dd

rises above the brown-out voltage. The

brown-out level is preset to approximately 4.2V at the

factory. See the FUSEX word register, BOR0 and BOR1

bits, for details.

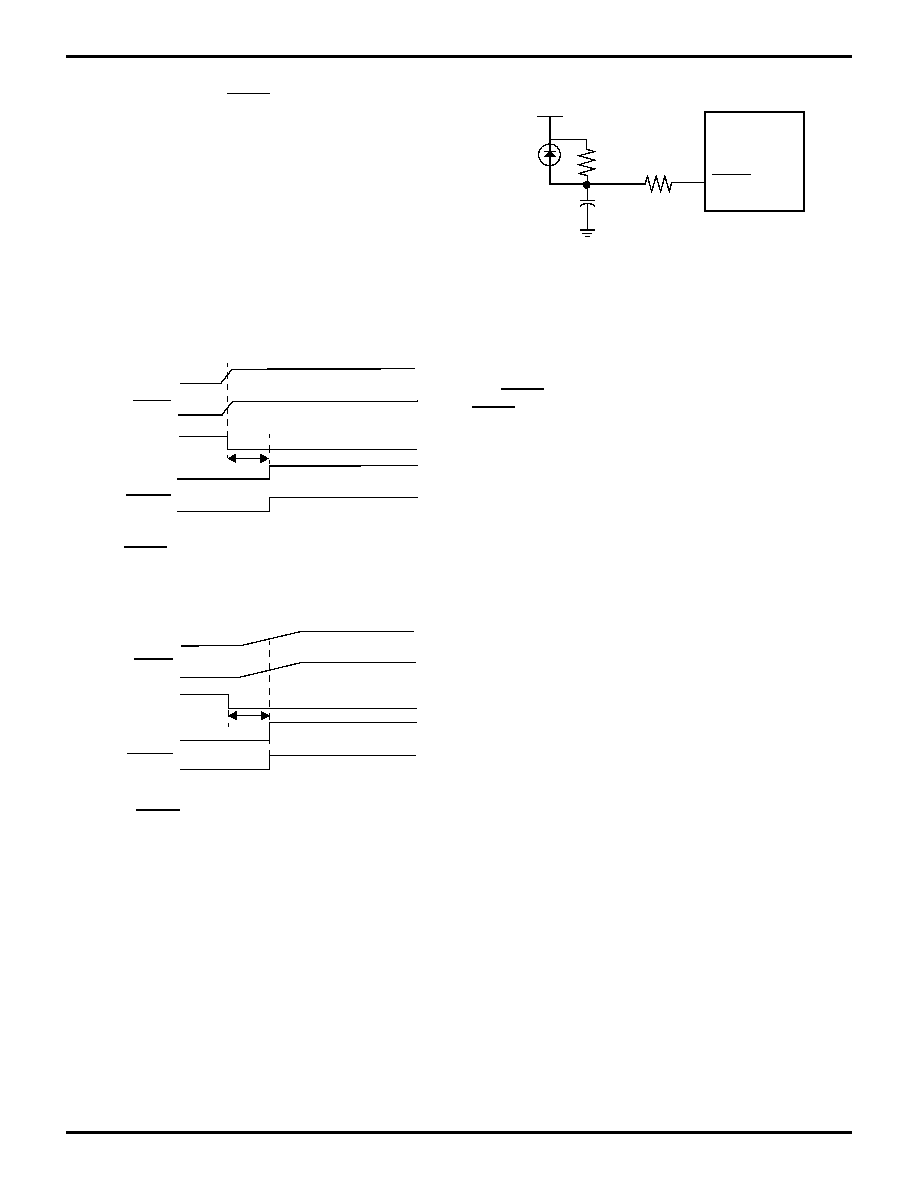

Figure 12-3. Time-out Sequence on Power-up

(MCLR tied to V

dd

): Fast V

dd

Rise Time

Figure 12-4. Time-out Sequence on Power-up

(MCLR tied to V

dd

): Slow Rise Time

V

dd

MCLR

POR

drt_time_out

RESET

Tdrt

V

dd

MCLR

POR

drt_time_out

RESET

Tdrt

V1

Figure 12-5. External Power-On Reset Circuit

(For Slow V

dd

Power-up)

V

dd

R

C

MCLR

D

R1