© 2005 Ubicom, Inc. All rights reserved.

- 12 -

www.ubicom.com

SX20AC/SX28AC

4.3 OPTION Register

(Write Only; program with MOV !OPTION, W command)

Upon reset, all bits in the OPTION register are set to 1.

RTW

RTE

_IE

RTS

RTE

_ES

PSA

PS2

PS1

PS0

Bit 7

Bit 0

RTW

RTCC/W register selection:

0 = Register 01h addresses W,

unless FUSEX bit 7 = 1

1 = Register 01h addresses RTCC

RTE_IE RTCC

edge

interrupt enable:

0 = RTCC roll-over interrupt is enabled,

unless FUSEX bit 7 = 1

1 = RTCC roll-over interrupt is disabled

RTS

RTCC increment select:

0 = RTCC increments on internal instruction

cycle

1 = RTCC increments upon transition on

RTCC pin

RTE_ES

RTCC edge select:

0 = RTCC increments on low-to-high transi-

tions

1 = RTCC increments on high-to-low transi-

tions

PSA

Prescaler Assignment:

0 = Prescaler is assigned to RTCC, with di-

vide rate determined by PS0-PS2 bits

1 = Prescaler is assigned to WDT, and divide

rate on RTCC is 1:1

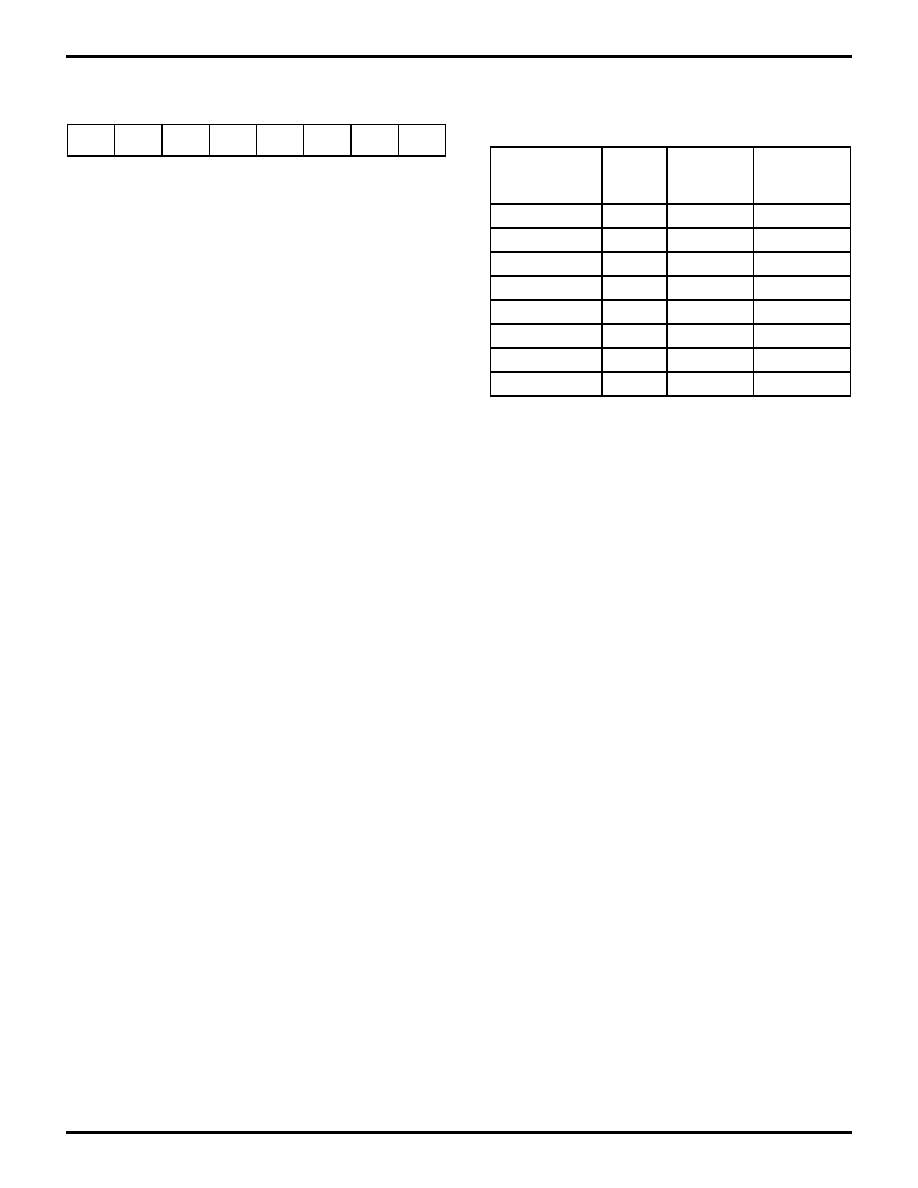

Table 4-2. Prescaler Divider Ratios

PS2, PS1, PS0

RTCC

Divide

Rate

Watchdog

Timer

Divide Rate

Approx.

Watchdog

Timeout (sec)

000

1:2

1:1

0.016

001

1:4

1:2

0.032

010

1:8

1:4

0.064

011

1:16

1:8

0.128

100

1:32

1:16

0.256

101

1:64

1:32

0.5

110

1:128

1:64

1.0

111

1:256

1:128

2.0