© 2005 Ubicom, Inc. All rights reserved.

- 11 -

www.ubicom.com

SX20AC/SX28AC

4.0 SPECIAL-FUNCTION REGISTERS

The CPU uses a set of special-function registers to con-

trol the operation of the device.

The CPU registers include an 8-bit working register (W),

which serves as a pseudo accumulator. It holds the sec-

ond operand of an instruction, receives the literal in

immediate type instructions, and also can be program-

selected as the destination register.

A set of 31 file registers serves as the primary accumula-

tor. One of these registers holds the first operand of an

instruction and another can be program-selected as the

destination register. The first eight file registers include

the Real-Time Clock/Counter register (RTCC), the lower

eight bits of the 11-bit Program Counter (PC), the 8-bit

STATUS register, three port direction registers for Port A,

Port B, Port C, the 8-bit File Select Register (FSR), and

INDF used for indirect addressing.

The five low-order bits of the FSR register select one of

the 31 file registers in the indirect addressing mode. Call-

ing for the file register located at address 00h (INDF) in

any of the file-oriented instructions selects indirect

addressing, which uses the FSR register. It should be

noted that the file register at address 00h is not a physi-

cally implemented register. The CPU also contains an 8-

level, 11-bit hardware push/pop stack for subroutine link-

age.

*In the SX20 package, Port C is not used, and address

07h is available as a general-purpose RAM location.

4.1 PC Register (02h)

The PC register holds the lower eight bits of the program

counter. It is accessible at run time to perform branch

operations.

4.2 STATUS Register (03h)

The STATUS register holds the arithmetic status of the

ALU, the page select bits, and the reset state. The

STATUS register is accessible during run time, except

that bits PD and TO are read-only. It is recommended

that only SETB and CLRB instructions be used on this

register. Care should be exercised when writing to the

STATUS register as the ALU status bits are updated

upon completion of the write operation, possibly leaving

the STATUS register with a result that is different than

intended. For instance, a CLR STATUS command will set

the Z bit as expected, but may leave bits 4, 3, 1, and 0

unchanged.

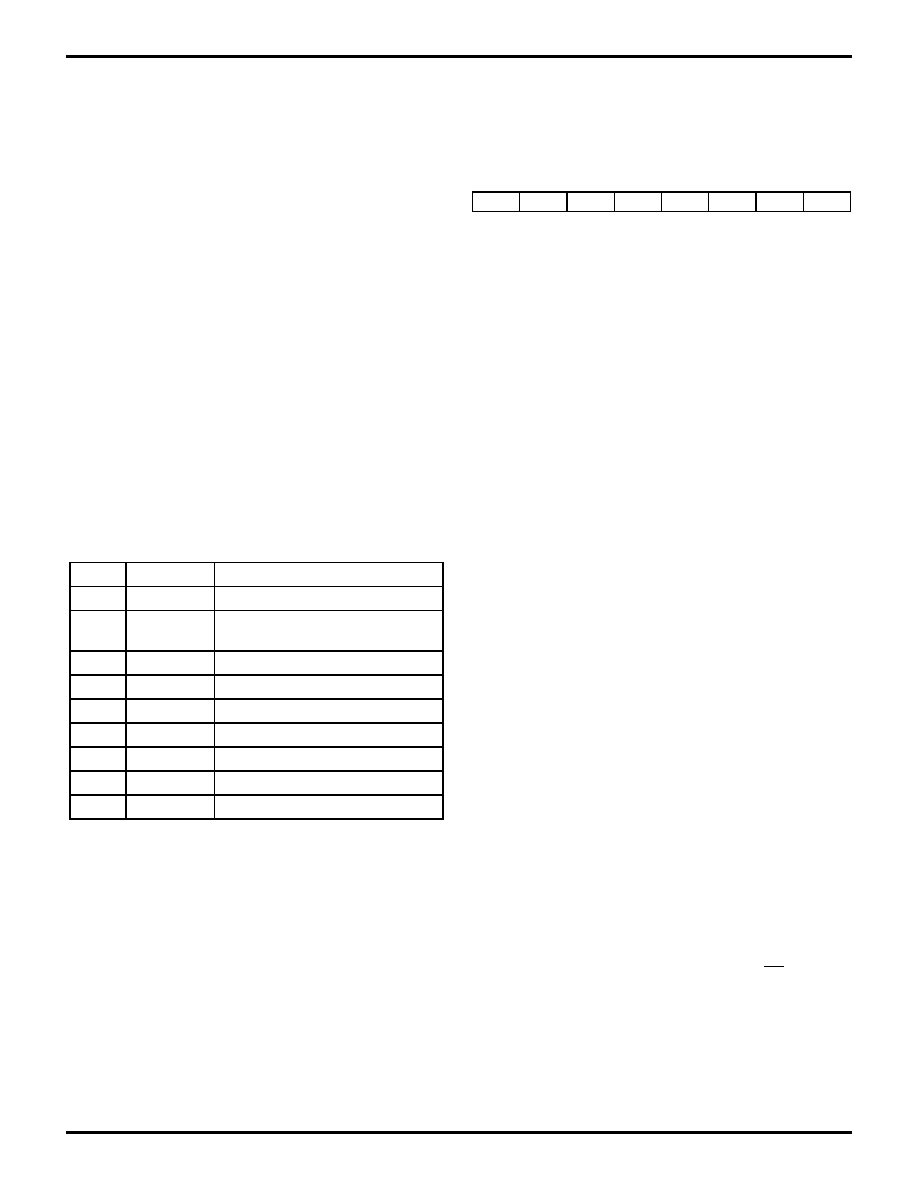

Table 4-1. Special-Function Registers

Addr

Name

Function

00h

INDF

Used for indirect addressing

01h

RTCC

Real Time Clock / Counter

(or W; see OPTION bit 7)

02h

PC

Program Counter (low byte)

03h

STATUS

Holds Status bits of ALU

04h

FSR

File Select Register

05h

RA

Port RA Data register

06h

RB

Port RB Data register

07h

RC*

Port RC Data register

08-0Fh

General Data RAM

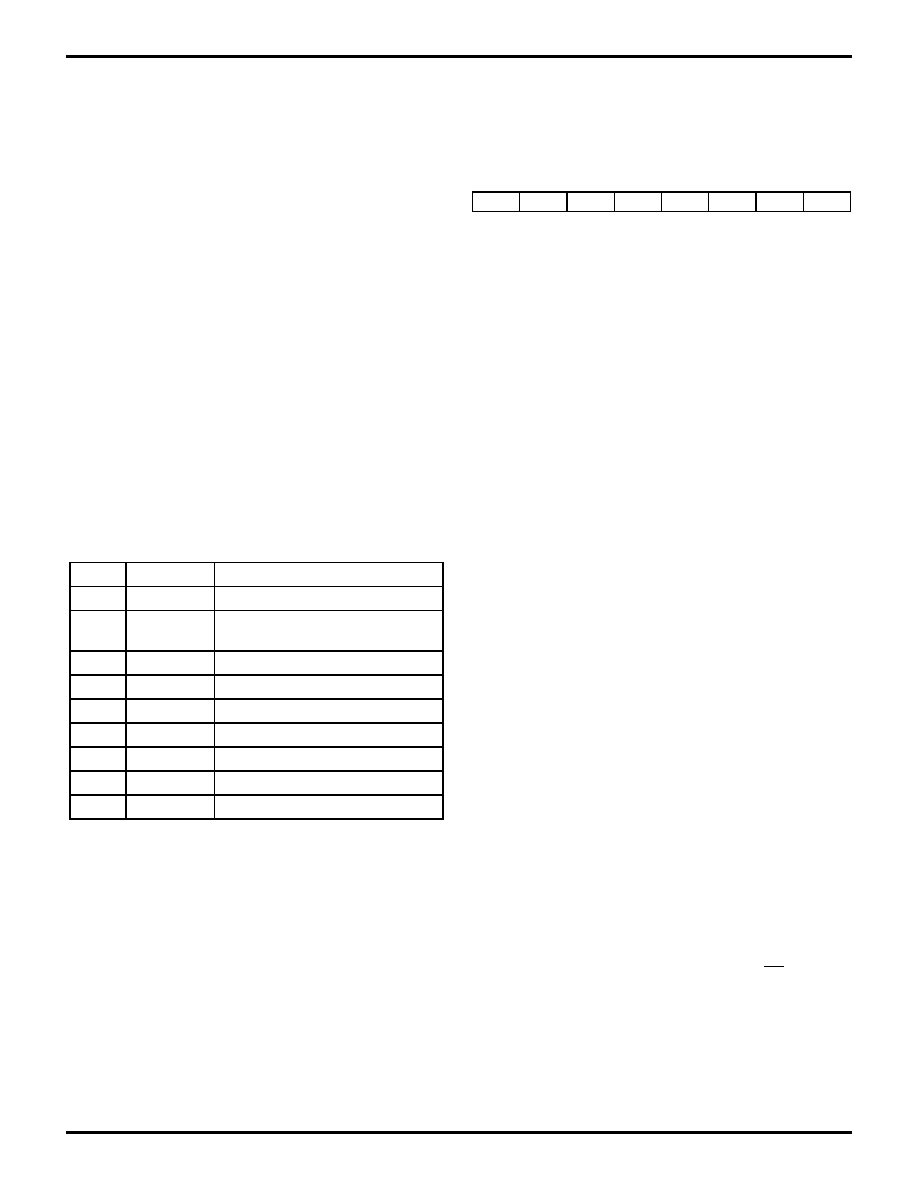

PA2

PA1

PA0

TO

PD

Z

DC

C

Bit 7

Bit 0

Bit 7-5: Page select bits PA2:PA0

000 = Page 0 (000h 01FFh)

001 = Page 1 (200h 03FFh)

010 = Page 2 (400h 05FFh)

011 = Page 3 (600h 07FFh)

Bit 4:

Time Out bit, TO (read only)

1 = Set to 1 after power up and upon exe-

cution of CLR !WDT or SLEEP instructions

0 = A watchdog time-out occurred

Bit 3:

Power Down bit, PD (read only)

1= Set to a 1 after power up and upon ex-

ecution of the CLR !WDT instruction

0 = Cleared to a `0' upon execution of

SLEEP instruction

Bit 2:

1 = Result of operation is zero

0 = Result of operation is non-zero

Bit 1:

After Addition:

1 = A carry from bit 3 occurred

0 = No carry from bit 3 occurred

After Subtraction:

1 = No borrow from bit 3 occurred

0 = A borrow from bit 3 occurred

Bit 0:

After Addition:

1 = A carry from bit 7 of the result occurred

0 = No carry from bit 7 of the result

occurred

After Subtraction:

1 = No borrow from bit 7 of the result

occurred

0 = A borrow from bit 7 of the result

occurred

Rotate (RR or RL) Instructions:

The carry bit is loaded with the low or high

order bit, respectively. When CF bit is

cleared, Carry bit works as input for ADD

and SUB instructions.