SX User’s Manual Rev. 3.1

140

© 2000 Scenix Semiconductor, Inc. All rights reserved.

www.scenix.com

Chapter 4 Clocking, Power Down, and Reset

4.5.2

Power-On Reset

In a typical power-on situation, the supply voltage takes a known (approximate) amount of time to rise

from zero volts to the final operating voltage. The SX device has an on-chip power-on reset circuit that

holds the device in the reset state until the supply voltage rises to a stable operating level, thus ensuring

reliable operation upon power-up.

The power-on reset circuit uses an asynchronous ripple counter to hold the device in the reset state for

a period of time as the supply voltage rises. This counter, called the Delay Reset Timer (DRT),

provides the device start-up delay. It is used only for a power-on reset, not for a reset caused by another

event such as a wakeup from the power down mode or a brown-out.

Upon power-up, the internal reset latch is set, which asserts the internal RESET signal and holds the

device in the reset state. The DRT counts clock pulses generated by the on-chip RC oscillator. It starts

counting when the RC oscillator starts working and a valid logic high signal is detected on the MCLR

input pin. When the DRT reaches the end of its timeout period (typically 72 msec), it clears the internal

reset latch, which releases the device from the reset state.

The MCLR (Master Clear Reset) input pin must be held low upon power-up of the device. If you do

not need to use the MCLR pin as a hardware reset input, you can simply tie it together with the VDD

power supply pin. This will work reliably only if the power supply rise time is significantly less than

the DRT delay of 72 msec.

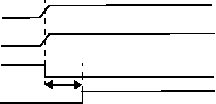

Figure 4-6 shows the power-on reset timing in this situation. The supply voltage and MCLR pin

voltages rise together, and the DRT counter allows the device to begin operating after a delay of about

72 msec.

Figure 4-7 shows the unacceptable situation where the supply voltage rises too slowly, and the device

is allowed to begin operating when the supply voltage has not yet reached a reliable level.

One solution to the situation shown in Figure 4-7 is to use an external RC delay circuit like the one

shown in Figure 4-8. This circuit holds the MCLR input low while the supply voltage rises. The values

of R and C should be chosen to cause a delay that exceeds the supply voltage rise time. R should be

less than 40 kW to ensure a sufficiently high voltage. The diode helps to discharge the capacitor quickly

when the power is turned off.

The power-on timing with the external RC network is shown in Figure 4-9. In this case, the device

comes out of reset about 72 msec after the MCLR input goes high.

Figure 4-6 Power-On Reset Timing (MCLR tied to VDD), Fast VDD Rise Time

VDD

MCLR

POR

drt_time_out

RESET

Tdrt