SX Device Programming Specifications Rev 2.2

6

© 2000 Scenix Semiconductor, Inc. All rights reserved.

www.scenix.com

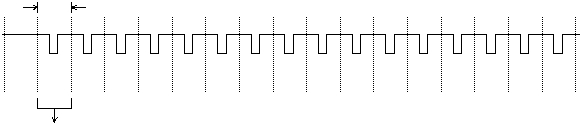

cycles to specify a programming operation such as “erase,” “read,” or “write.” The command cycles

are followed by 12 “data” cycles, designated D11 through D0. During these cycles, the programmer

unit drives the OSC2 pin for a “write” operation, or the SX device drives the pin for a “read” operation.

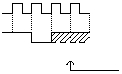

Each of the 17 cycles consists of four internal clock periods.

In the first clock period, nothing drives the OSC2 pin, so the pin is pulled high by an internal pullup

resistor.

In the second clock period, the SX device drives the OSC2 pin low. This is the synchronization pulse.

The external programming unit uses the leading edge of this pulse to synchronize itself to the SX

device. The pulse is omitted in the sync cycle (the first of 17 cycles in a frame) so that the programming

unit can determine where the frame starts.

In the third and fourth clock periods, the programmer unit writes a data bit to the SX device or reads a

data bit from the SX device, depending on the cycle and the type of command issued. The data bit is

placed on the OSC2 pin during these two clock periods, either by the programmer unit or by the SX

device, and then sampled by on the rising edge of the fourth clock period.

In the four command cycles (C3-C0), the programmer writes a four-bit command to the ISP logic,

which tells the ISP logic what to do during the data cycles. In the 12 data cycles (D11-D0), for a “write”

operation, the programmer writes the 12 bits that are to be written to a memory location. For a “read”

operation, the programmer reads 12 bits supplied by the SX device from a memory location.

Figure 2.3 ISP Frame

In System Programming Protocol

sync

C3

C2

C1

C0

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

1 frame

1 cycle

0

1

2

3

4 clocks per cycle

data is sampled at

this edge

ISP Commands:

nop

4'hf

erase

4'h0

read_dev

4'h1

read_fusex

4'h2

prog_fusex

4'h3

Load

4'h4

prog

4'h5

read

4'h6

inc

4'h7