© 2000 Scenix Semiconductor, Inc. All rights reserved.

- 1 -

www.scenix.com

Scenix™ and the Scenix logo are trademarks of Scenix Semiconductor, Inc.

I2C™ is a trademark of Philips Corporation

Microwire™ is a trademark of National Semiconductor Corporation

All other trademarks mentioned in this document are property of their respec-

tive companies.

January 19, 2000

SX18AC/SX20AC/SX28AC/SX18AC75/SX20AC75/SX28AC75

Configurable Communications Controllers with EE/Flash Program

Memory, In-System Programming Capability and On-Chip Debug

1.0

PRODUCT OVERVIEW

1.1 Introduction

The Scenix SX family of configurable communications

controllers are fabricated in an advanced CMOS process

technology. The advanced process, combined with a

RISC-based architecture, allows high-speed computa-

tion, flexible I/O control, and efficient data manipulation.

Throughput is enhanced by operating the device at fre-

quencies up to 50/75 MHz and by optimizing the instruc-

tion set to include mostly single-cycle instructions. In

addition, the SX architecture is deterministic and totally

reprogramable. The unique combination of these charac-

teristics enables the device to implement hard real-time

functions as software modules (Virtual Peripheral™) to

replace traditional hardware functions.

On-chip functions include a general-purpose 8-bit timer

with prescaler, an analog comparator, a brown-out detec-

tor, a watchdog timer, a power-save mode with multi-

source wakeup capability, an internal R/C oscillator, user-

selectable clock modes, and high-current outputs.

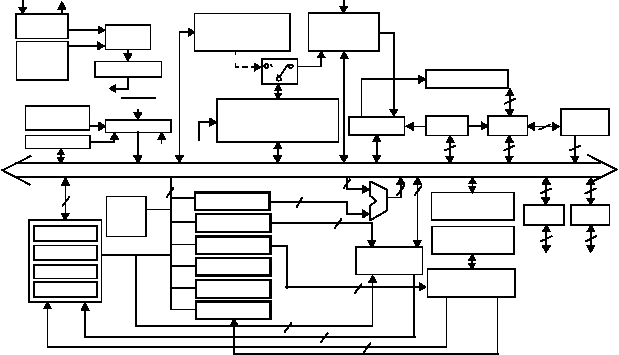

Figure 1-1. Block Diagram

Interrupt

MIW U

Port B

Comp

Power-O n

Reset

RESET

8-bit W atchdog

Tim er (W DT)

8-bit Tim er

RTCC

8

8

8

Port C

8

8

Port A

8

4

Internal Data Bus

In-System

Debugging

In-System

Programm ing

2k W ords

EEPRO M

System

Clock

Brown-O ut

MIW U

M CLR

O SC

Driver

4M Hz

Internal

RC OSC

Clock

Select

¸ 4 or ¸ 1

136 Bytes

SRAM

Address

W rite Data

Read Data

Instruction

W

FSR

STATUS

PC

M O DE

OPTIO N

System Clock

OSC1 O SC2

Fetch

8

8

12

Address

12

8

8

8

8

ALU

8

8

8

3

RTCC

Analog

8

Interrupt Stack

PC

3 Level

Decode

Executive

W rite Back

IREAD

Stack

Instruction

Pipeline

Prescaler for RTCC

or

Prescaler for W DT