© 1999 Scenix Semiconductor, Inc. All rights reserved.

- 18 -

www.scenix.com

SX18AC / SX20AC / SX28AC

8.0

INTERRUPT SUPPORT

The device supports both internal and external maskable

interrupts. The internal interrupt is generated as a result

of the RTCC rolling over from 0FFh to 00h. This interrupt

source has an associated enable bit located in the

OPTION register. There is no pending bit associated with

this interrupt.

Port B provides the source for eight external software

selectable, edge sensitive interrupts. These interrupt

sources share logic with the Multi-Input Wakeup circuitry.

The WKEN_B register allows interrupt from Port B to be

individually enabled or disabled. Clearing a bit in the

WKEN_B register enables the interrupt on the corre-

sponding Port B pin. The WKED_B selects the transition

edge to be either positive or negative. The WKEN_B and

WKED_B registers are set to FFh upon reset. Setting a

bit in the WKED_B register selects the falling edge while

clearing the bit selects the rising edge on the correspond-

ing Port B pin.

The WKPND_B register serves as the external interrupt

pending register.

The WKPND_B register comes up a with random value

upon reset. The user program must clear the WKPND_B

register prior to enabling the interrupt. The proper

sequence is described in Section 7.2

.

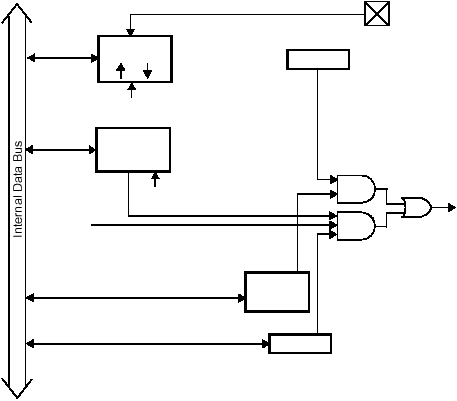

Figure 8-1 shows the structure of the interrupt logic.

Figure 8-1. Interrupt Structure

RTCC

WKED_B

WKED_B

WKPND_B

WKPND_B

From MODE

(MODE = 09)

OPTION

RTE_IE

WKEN_B

1 = Ext. Interrupt through Port B

0 = Power Down Mode, no Ext. Interrupt

STATUS

Port B PIN

Interrupt

PC

Interrupt Stack

PC

000

Overflow

Register

PD bit

From MODE

(MODE = 0A)