© 1999 Scenix Semiconductor, Inc. All rights reserved.

- 25 -

www.scenix.com

SX18AC / SX20AC / SX28AC

12.0 RESET

Power-On-Reset, Brown-Out reset, watchdog reset, or

external reset initializes the device. Each one of these

reset conditions causes the program counter to branch to

the top of the program memory. For example, on the

device with 2048K words of program memory, the pro-

gram counter is initialized to 07FF.

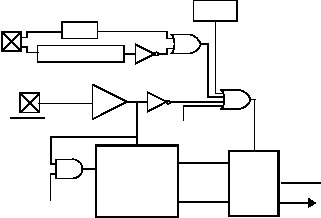

The device incorporates an on-chip Power-On Reset

(POR) circuit that generates an internal reset as Vdd rises

during power-up. Figure 12-1 is a block diagram of the

circuit. The circuit contains an 10-bit Delay Reset Timer

(DRT) and a reset latch. The DRT controls the reset time-

out delay. The reset latch controls the internal reset sig-

nal. Upon power-up, the reset latch is set (device held in

reset), and the DRT starts counting once it detects a valid

logic high signal at the MCLR pin. Once DRT reaches the

end of the timeout period (typically 72 msec), the reset

latch is cleared, releasing the device from reset state.

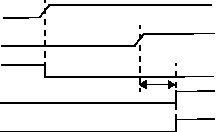

Figure 12-2 shows a power-up sequence where MCLR is

not tied to the Vdd pin and Vdd signal is allowed to rise

and stabilize before MCLR pin is brought high. The

device will actually come out of reset Tdrt msec after

MCLR goes high.

The brown-out circuitry resets the chip when device

power (Vdd) dips below its minimum allowed value, but

not to zero, and then recovers to the normal value.

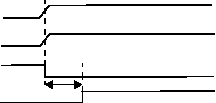

Figure 12-3 shows the on-chip Power-On Reset

sequence where the MCLR and Vdd pins are tied

together. The Vdd signal is stable before the DRT time-

out period expires. In this case, the device will receive a

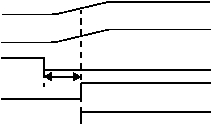

proper reset. However, Figure 12-4 depicts a situation

where Vdd rises too slowly. In this scenario, the DRT will

time-out prior to Vdd reaching a valid operating voltage

level (Vdd min). This means the device will come out of

reset and start operating with the supply voltage not at a

valid level. In this situation, it is recommended that you

use the external RC circuit shown in Figure 12-5. The RC

delay should exceed the time period it takes Vdd to reach

a valid operating voltage.

Note 1: The external Power-On Reset circuit is required

only if Vdd power-up is too slow. The diode D helps dis-

charge the capacitor quickly when Vdd powers down.

Note 2: R < 40 kW is recommended to make sure that

voltage drop across R does not violate the device electri-

cal specifications.

Note 3: R1 = 100W to 1kW will limit any current flowing

into MCLR from external capacitor C. This helps prevent

Note:Ripple counter is 10 bits for Power on Reset (POR)

only.

Figure 12-1. Block Diagram of On-Chip Reset Circuit

POR

BROWN-OUT

MIWU

MCLR/Vpp pin

wdt_time_out

10-Bit Asynch

Ripple

Counter

(DRT Start-Up

Timer)

Vdd

rc_clk

drt_time

_out

S

R

Q

QN

RESET

POR

enable

Figure 12-2. Time-Out Sequence on Power-Up

(MCLR not tied to Vdd)

Figure 12-3. Time-out Sequence on Power-up

(MCLR tied to Vdd): Fast Vdd Rise Time

Figure 12-4. Time-out Sequence on Power-up

(MCLR tied to Vdd): Slow Rise Time

Vdd

MCLR

POR

drt_time_out

RESET

Tdrt

Vdd

MCLR

POR

drt_time_out

RESET

Tdrt

Vdd

MCLR

POR

drt_time_out

RESET

Tdrt

V1