© 1999 Scenix Semiconductor, Inc. All rights reserved.

- 22 -

www.scenix.com

SX18AC / SX20AC / SX28AC

10.0

REAL TIME CLOCK

(RTCC)/WATCHDOG TIMER

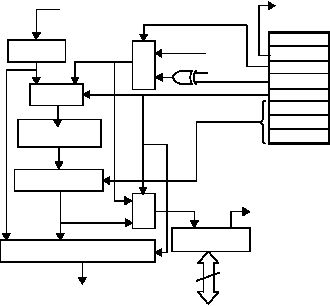

The device contains an 8-bit Real Time Clock/Counter

(RTCC) and an 8-bit Watchdog Timer (WDT). An 8-bit

programmable prescaler extends the RTCC to 16 bits. If

the prescaler is not used for the RTCC, it can serve as a

postscaler for the Watchdog Timer. Figure 10-1 shows

the RTCC and WDT block diagram.

10.1

RTCC

RTCC is an 8-bit real-time timer that is incremented once

each instruction cycle or from a transition on the RTCC

pin. The on-board prescaler can be used to extend the

RTCC counter to 16 bits.

The RTCC counter can be clocked by the internal instruc-

tion cycle clock or by an external clock source presented

at the RTCC pin.

To select the internal clock source, bit 5 of the OPTION

register should be cleared. In this mode, RTCC is incre-

mented at each instruction cycle unless the prescaler is

selected to increment the counter.

To select the external clock source, bit 5 of the OPTION

register must be set. In this mode, the RTCC counter is

incremented with each valid signal transition at the RTTC

pin. By using bit 4 of the OPTION register, the transition

can be programmed to be either a falling edge or rising

edge. Setting the control bit selects the falling edge to

increment the counter. Clearing the bit selects the rising

edge.

The RTCC generates an interrupt as a result of an RTCC

rollover from 0FF to 000. There is no interrupt pending bit

to indicate the overflow occurrence. The RTCC register

must be sampled by the program to determine any over-

flow occurrence.

10.2

Watchdog Timer

The watchdog logic consists of a Watchdog Timer which

shares the same 8-bit programmable prescaler with the

RTCC. The prescaler actually serves as a postscaler if

used in conjunction with the WDT, in contrast to its use as

a prescaler with the RTCC.

10.3

The Prescaler

The 8-bit prescaler may be assigned to either the RTCC

or the WDT through the PSA bit (bit 3 of the OPTION reg-

ister). Setting the PSA bit assigns the prescaler to the

WDT. If assigned to the WDT, the WDT clocks the pres-

caler and the prescaler divide rate is selected by the

PS0, PS1, and PS2 bits located in the OPTION register.

Clearing the PSA bit assigns the prescaler to the RTCC.

Once assigned to the RTCC, the prescaler clocks the

RTCC and the divide rate is selected by the PS0, PS1,

and PS2 bits in the OPTION register. The prescaler is not

mapped into the data memory, so run-time access is not

possible.

The prescaler cannot be assigned to both the RTCC and

WDT simultaneously.

Figure 10-1. RTCC and WDT Block Diagram

WDTE (from FUSE Word)

RTCC pin

MUX

8-Bit Prescaler

MUX (8 to 1)

8-Bits

WDT Time-out

Data Bus

WDT

MUX

M

RTCC

M

U

X

FOSC

RST

RTE_ES

PSA

PS2

PS1

PS0

OPTION

Register

RTCC Rollover

Interrupt

RTE_IE

RTW

RTCC

Interrupt

Enable

U

X