IP2022 Data Sheet

www.ubicom.com

73

•

CMP_RES—set if last LFSR operation result

matched contents of RESCMP register.

•

SHIFT_COUNT3:0—specifies number of bits to shift,

load with N for an operation of N+1 shifts.

5.9.2

LFSRCFG2 Register

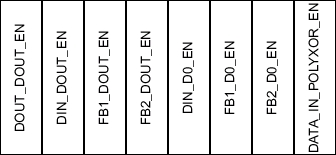

Figure 5-22 LFSRCFG2 Register

•

DOUT_DOUT_EN—set to enable DOUT multiplexer

output in source gating for DOUT node.

•

DIN_DOUT_EN—set to enable DIN signal in source

gating for DOUT node.

•

FB1_DOUT_EN—set to enable FB1 signal in source

gating for DOUT node.

•

FB2_DOUT_EN—set to enable FB2 signal in source

gating for DOUT node.

•

DIN_D0_EN—set to enable DIN signal in source gat-

ing for D0 node.

•

FB1_D0_EN—set to enable FB1 signal in source gat-

ing for D0 node.

•

FB2_D0_EN—set to enable FB2 signal in source gat-

ing for D0 node.

•

DATA_IN_POLYXOR_EN—set to enable DIN signal

in source gating for POLY_XOR_EN node.

5.9.3

LFSRCFG3 Register

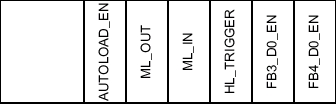

Figure 5-23 LFSRCFG3 Register

•

AUTOLOAD_EN—set to enable autoloading DATAIN

register when SxRBUF register of corresponding

SERDES unit is loaded.

•

ML_OUT—set to shift data out of residue register

LSB, and into MSB, clear to shift data out of residue

register MSB, and into LSB. See Figure 5-19 for effect

on RESx mapping.

•

ML_IN—set to shift data from DATAIN register MSB-

first to DIN node, clear to shift data LSB-first.

•

HL_TRIGGER—set to trigger operation start on load-

ing DATAINH register, clear to trigger on DATAINL.

•

FB3_D0_EN—set to enable FB3 signal in source gat-

ing for D0 node.

•

FB4_D0_EN—set to enable FB4 signal in source gat-

ing for D0 node.

5.9.4

DATAIN Register

The 8-bit DATAINH and DATAINL registers together

comprise the 16-bit DATAIN register. For LFSR0 and

LFSR2, the AUTOLOAD_EN bit in the LFSRCFG3

register can be used to enable automatic loading from

SERDES1. For LFSR1 and LFSR3, the AUTOLOAD_EN

bit in the LFSRCFG3 register can be used to enable

automatic loading from SERDES2. The HL_TRIGGER bit

in the LFSRCFG3 register controls whether loading the

DATAINH or DATAINL register triggers the start of the

LFSR operation. The ML_IN bit in the LFSRCFG3 register

controls whether data is shifted MSB-first or LSB-first from

the DATAIN register to the DIN node.

5.9.5

DATAOUT Register

The 8-bit DATAOUTH and DATAOUTL registers together

comprise the 16-bit DATAOUT register. Data shifted out of

the residue register is shifted LSB-first into the DATAOUT

register.

5.9.6

DOUT Register

The DOUT register controls a 40:1 multiplexer on the

residue register outputs. It selects a term which can be

used in the source gating for the DOUT bit stream.

5.9.7

FBx Registers

The four FBx registers control four 40:1 multiplexers on

the residue register outputs. They select feedback terms

which can be used in the source gating for the D0,

POLY_XOR_EN, and DOUT bit streams.

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

Reserved