68

www.ubicom.com

IP2022 Data Sheet

5.7

Analog to Digital Converter (ADC)

The on-chip A/D converter has the following features:

•

10-bit ADC, ½ LSB accuracy

•

8 input channels

•

48 kHz maximum sampling rate

•

One-shot conversion.

•

Optional external reference voltage

•

Vmax = AVdd (max 2.7V)

•

Result returned in the ADCH and ADCL registers

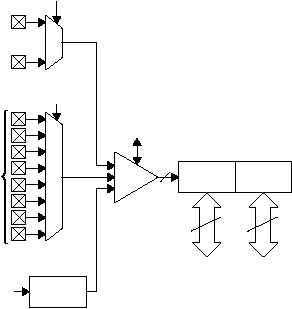

Figure 5-16 shows the A/D converter circuitry. The ADC

input pins use alternate functions of the Port G pins. The

result of an ADC sample is the analog value measured on

the selected pin. To correctly read an external voltage, the

pin being sampled must be configured as an input in the

port direction register (i.e. the RGDIR register). If the pin

is configured as an output, then the result will indicate the

voltage level being driven by the output buffer. The RG1

and RG2 port pins are also used as the analog

comparator input pins. The result of sampling the RG1 or

RG2 pins will be correct whether or not the comparator is

operating. The RG0 pin is also used as the comparator

output pin. If the comparator is enabled, then sampling the

RG0 pin will indicate the voltage level being driven by the

comparator. The RG3 pin is multiplexed with the external

reference voltage.

Figure 5-16 A/D Converter Block Diagram

5.7.1

ADC Reference Voltage

The reference voltage (Vref) can come from either the

RG3 port pin or from the AVdd supply voltage. If AVdd is

used, the RG3 port pin may be used as a channel of

analog input or as a general-purpose port pin.

Vref defines a voltage level which reads as one increment

of resolution below the full-scale voltage. The full-scale

voltage reads as 0x3FF, so the Vref voltage reads as

0x3FE and the A/D converter resolution is 10 bits. Table

5-13 shows the values reported at the upper and lower

limits of the ADC input voltage range.

5.7.2

A/D Converter Registers

ADCTMR Register

The ADCTMR register (see Section 7.1.2) is used to

specify the number of system clock cycles required for a

delay of 1736 ns, which is used to provide the 1.152MHz

(48 kHz × 24) clock period reference clock for the A/D

converter.

At a system clock frequency of 120 MHz, the timer register

should be set to 53 ((120 MHz/1.152 MHz)/2). The

minimum value that may be loaded into the ADCTMR

register is 2, so the system clock must be at least 24 times

the ADC sampling frequency for the ADC to function.

ADCCFG Register

The A/D converter configuration register (ADCCFG)

provides the control and status bits for the A/D converter,

as shown in Section 7.1.1.

515-016.eps

ADCH

A/D

Vref

Reference

Voltage

ADCREF

ADC Timer

8

7

0

ADCGO

10

ADCL

8

7

0

AVdd

RG7:0

System

Clock

ADCS2:0

RG3

Data Bus Data Bus

Table 5-13 ADC Values

Vin Voltage

ADC Value

0V

0x000

Vref/0x3FE

0x001

Vref

0x3FE

Vref + (Vref/0x3FE)

0x3FF