66

www.ubicom.com

IP2022 Data Sheet

5.6.10 GPSI

Hardware

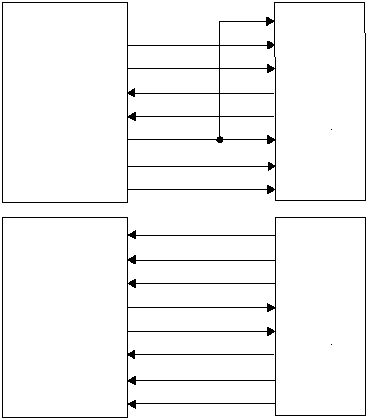

Figure 5-15 shows example circuits to connect the

SERDES in GPSI mode. Table 5-11 shows the GPSI

signal to port pin mapping in Master mode, and Table 5-

12 shows the GPSI signal to port pin mapping in Slave

mode.

Software

GPSI is a general-purpose, point-to-point, full-duplex

serial bus protocol. Only two devices are allowed to exist

on a bus. The GPSI PHY device is responsible for

maintaining bus timing by driving two continuously

running clocks, TxClk and RxClk. The device that does

not drive the clocks is the MAC device. The TxEn and TxD

signals are synchronized to the TxClk clock. The RxD and

RxEn signals are synchronized to the RxClk clock.

The COLLISION and TxBUSY signals do not participate in

actual data transfer on the GPSI bus. The COLLISION

signal is connected to a GPIO port pin, and TxBUSY is

connected to the SxTXME to provide additional flow

control capabilities for the software device driver. The

COLLISION signal is used to indicate that a PHY device

has detected a collision condition. This signal is only

useful when the SERDES is connected to a PHY device

or acting as a PHY device.

The TxBUSY signal is used by a GPSI device to indicate

that the device is currently busy, and that another device

should not attempt to start a data transfer. COLLISION

and TxBUSY are asynchronous to both TxClk and RxClk.

TxBUSY can be configured as either an input or an output

depending which device is slower and has a need to stall

incoming data.

Figure 5-15 GPSI Interface Examples

515-096a.eps

OR

GPSI

Master

SxCLK

IP2022

(GPSI Slave)

SxTXP

RxCLK

RxD

SxRXD

TxD

SxRXP

TxEN

SxTXPE

RxEN

SxTXM

TxCLK

GPIO

COL

SxTXME

TxBUSY

GPSI

Slave

IP2022

(GPSI Master)

SxTXP

RxCLK

TxD

SxRXD

RxD

SxRXP

RxEN

SxTXPE

TxEN

SxTXM

TxCLK

GPIO

COL

SxTXME

TxBUSY

RxCLK

TxD

RxD

RxEN

TxEN

TxCLK

COL

TxBUSY

RxCLK

RxD

TxD

TxEN

RxEN

TxCLK/RxCLK

COL

TxBUSY