IP2022 Data Sheet

www.ubicom.com

57

For transmitting, software must specify the number of bits

to transmit (specified in the SxTCFG register) and load

the data in the SxTBUF register. This data is then

transferred to an internal register, from which it is serially

shifted out to the transmit logic. The TXBE bit in the

SxINTE register can be set to enable an interrupt when

the data has been transferred from the SxTBUF register.

When there is a transmit buffer underrun event (i.e. all of

the data has been shifted out from the internal register, but

the SxTBUF register has not been reloaded), an EOP

condition is generated on the SxTXP and SxTXM outputs

after an internal counter decrements to zero. The TXEOP

bit in the SxINTE register can be set to enable an interrupt

when an underrun event occurs.

For protocols other than USB and Ethernet, the EOP

generator is bypassed.

5.6.4

SERDES Interrupts

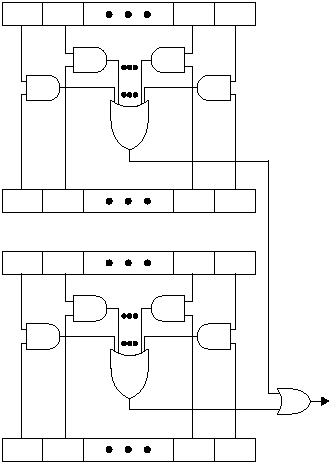

Figure 5-10 shows the interrupt logic for the two SERDES

units. For a detailed description of the SxINTE/SxINTF

register bits, refer to Section 7.1.10.

Figure 5-10 SERDES Interrupt Logic

515-041.eps

S1INTF Register

S1INTE Register

Serializer/

Deserializer

Interrupt

S0INTF Register

S0INTE Register