IP2022 Data Sheet

www.ubicom.com

55

5.6

Serializer/Deserializer (SERDES)

There are two SERDES units in the IP2022, which support

a variety of serial communication protocols, including

GPSI, SPI, UART, USB, and 10Base-T Ethernet. By

performing data serialization/deserialization in hardware,

the

CPU

bandwidth

needed

to

support

serial

communication is greatly reduced, especially at high baud

rates. Providing two units allows easy implementation of

protocol conversion or bridging functions, such as a USB

to 10Base-T Ethernet bridge.

Each SERDES unit uses up to 8 external digital signals:

SxCLK, SxRXD, SxRXM, SxRXP, SxTXM, SxTXME,

SxTXP, and SxTXPE/SxOE. The signals for SERDES1

are multiplexed with the Port E pins, and the signals for

SERDES2 are multiplexed with the Port F pins. The port

direction bits must be set appropriately for each pin that is

used. The SxOE signal is multiplexed with the SxTXPE

signal. Not all signals are used in all protocol modes. See

Table 5-4 for details on signal port pin usage in various

protocol modes. In addition to the digital signals, there are

also two analog signals only used in 10Base-T Ethernet

mode: SxRX+ and SxRX-.

Note: Proper operation of the SERDES requires that the

core-clock be present - don’t turn off core clock while

SERDES is still transmitting.

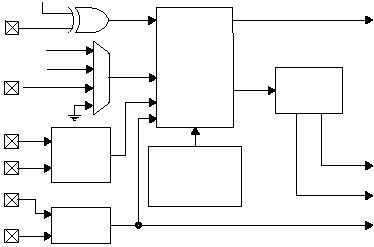

Figure 5-7 shows the clock/data separation and End-of-

Packet (EOP) detection logic of a SERDES unit. In USB

mode, the SxRXD input carries the data received from an

external transceiver. The SxRXP and SxRXM pins

correspond to the differential inputs of the USB bus.

Providing both inputs allows sensing of an EOP condition.

The SxRXD input is also used for interfaces with single-

ended input (i.e. GPSI, SPI, and UART modes), in which

case the clock/data separation circuit does not modify the

data. For 10Base-T Ethernet, a differential line receiver is

provided.

Figure 5-7 Clock/Data Separation and EOP Detection

5.6.1

SERDES Configuration Registers

The descriptions for the SxMODE, SxRSYNC, SxSMASK,

SxRCFG, SxRCNT, SxTCFG, SxTMRH/SxTMRL and

SxINTE/SxINTF registers can be found in Section 7.1.

Note: Delay needed when writing to SerDes registers

when using OSC clock

5.6.2

SERDES TX/RX Buffers

SxRBUFH/SxRBUFL Registers

16-bit register pair for unloading received data. The RXBF

bit in the SxINTF register indicates when new data has

been loaded into this register. If the corresponding bit in

the SxINTE register is set, an interrupt is generated.

515-003c.eps

Clock/Data

Separation

and

Start

Condition

Detection

Receive Polarity

Reversal Bit

Receive

Clock

Receive

Data

Transmit

Clock

Clock

Data

EOP

UART Clock

Divider

EOP

Detection

Synchronization

Pattern

Register

(SxRSYNC)

SxRXP

Input

SxRXD

Input

post-PLL Clock

OSC Clock

SxRXM

Input

Ethernet

Squelch

Circuit

SxRx+

SxRx-

SxCLK