54

www.ubicom.com

IP2022 Data Sheet

high 8 bits come from the value being written to the

TxCAP2H register. Software should write the TxCAP2L

register before writing the TxCAP2H register, because

writing to the TxCAP2H register is used as an indication

that a new compare value has been written. Writing to the

TxCAP2H register is required for the new compare value

to take effect. In PWM mode, the 16-bit number latched

into the internal compare register by writing to the

TxCAP2H register does not take effect until the end of the

current PWM cycle.

Reading the TxCAP2H or TxCAP2L registers returns the

previously written value regardless of whether the value

stored in these registers has been transferred to the

internal compare register by writing to the TxCAP2H

register.

In Capture/Compare mode, this register captures the

value of the counter/timer when the TxCPI2 input is

triggered. In this mode, this register is read-only.

Reading the TxCAP2L register returns the least-

significant 8 bits of an internal capture register and causes

the most-significant 8-bits to be latched into the TxCAP2H

register. This allows software to read the TxCAP2H

register later and still be assured of atomicity.

TxCFG1H/TxCFG1L Register

Selects timer operation mode, pin functions, interrupts

and other configuration settings. See Section 7.1.21 for

the description of TxCFG1H and Section 7.1.23 for the

description of TxCFG1L.

TxCFG2H/TxCFG2L Register

Selects capture input trigger edges, prescaler setting, and

other configuration settings. See Section 7.1.22 for the

description of TxCFG2H and Section 7.1.24 for the

description of TxCFG2L.

TCTRL Register

Unlike the other timer control registers, one TCTRL

register is used to synchronize both timers. Setting the

TxRST bit clears the TxCNTH/TxCNTL register pair and

the

prescaler

counter,

which

allows

global

synchronization of all timers on the device. There are also

individual timer interrupt-enable bits. See Section 7.1.25

for description.

5.5

Watchdog Timer

A Watchdog Timer is available for recovering from

unexpected system hangups. When the Watchdog Timer

is enabled, software must periodically clear the timer by

executing a cwdt instruction. Otherwise, the timer will

overflow, which resets the IP2022 and sets the WD bit in

the PSPCFG register. Any other source of reset clears the

WD bit, so software can use this bit to identify a reset

caused by the Watchdog Timer. The Watchdog Timer is

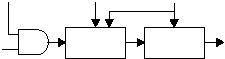

shown in Figure 5-6.

Figure 5-6 Watchdog Timer

The Watchdog Timer is enabled by setting the WDTE bit

in the FUSE1 register. The time period between coming

out of reset or clearing the timer and timer overflow is

controlled by the WDPS2:0 bits in the FUSE1 register, as

shown in Table 5-2.

The Watchdog Timer register is not visible to software.

The only feature of the Watchdog Timer visible to software

is the WD bit in the PSPCFG register (see Section 7.1.8).

Note: When using the development tools, the watchdog

timer is disabled while in debug mode, except when “Run”

command is issued.

Table 5-2 Watchdog Timer Period

WDPS2:0 (FUSE1 register)

Period (ms)*

000

~20

001

~40

010

~80

011

~160

100

~320

101

~640

110

~1280

111

~2560

* Time periods are approximate

515-076.eps

8-Bit

Timer

Watchdog

Timer Reset

Prescaler

Internal

RC Clock

(15 kHz)

WDTE

WDPS 2:0

cwdt Instruction