IP2022 Data Sheet

www.ubicom.com

49

5.2

Timer 0

Timer 0 is an 8-bit timer with an 8-bit prescaler intended to

generate periodic interrupts for ipModule™ instances that

require being called at a constant rate, such as UART and

DTMF functions. When the T0TMR register counts up to

FF and rolls over to 00, the T0IF flag in the T0CFG

register will be set, and an interrupt will occur if the T0IE

and T0EN bit are set (see T0CFG register description in

Section 7.1.20). To clear the interrupt, either the T0IE or

T0EN bit should be cleared , and then the T0IF flag must

be cleared.

Note: If T0IF is not cleared after disabling the Timer0

interrupt (T0IE = 0) or disabling Timer0 (T0EN = 0), it is

assumed that another interrupt has occured, and the

interrupt will occur on the next return, or when GIE is set

(enabling nested interrupts - see Section 3.7.2).

The Timer 0 interrupt is also supported in the instruction

set by an option for the reti instruction which adds the

W register to the T0TMR register when returning from an

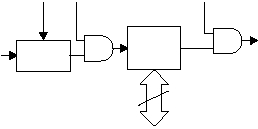

interrupt. Figure 5-3 shows the Timer 0 logic.

Operation of Timer 0 to generate periodic interrupts:

•

T0TMR = 00 when entering ISR from T0 interrupt

•

Keeps counting up while in ISR

•

Add W to T0TMR with execution of ret -W at the end

of ISR. Interrupt frequency is adjusted by adjusting

value loaded in W, and depending on core clock divid-

er, since T0TMR runs system clock.

Note: Do not enable Timer 0 interrupt before enabling the

Timer 0 itself.

Figure 5-3 Timer 0 Block Diagram

The control and status register for Timer 0 is the T0CFG

register, described in detail in Section 7.1.20.

Note: T0IF can only be asserted when T0IE = 1, T0EN =

1 and T0TMR overflow occurs.

515-091c.eps

8-bit

T0TMR

Register

Data Bus

T0IE

T0IF

8-Bit

Prescaler

8

System

Clock

T0EN

T0PS 3:0