34

www.ubicom.com

IP2022 Data Sheet

4.1.4

Indirect-with-Offset Addressing

Mode

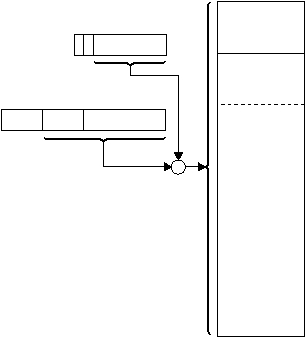

The indirect-with-offset addressing mode is used when bit

8 of the “fr” field is set. The location of the operand is

specified by a 7-bit unsigned immediate from the “fr” field

added to a 12-bit base address in a pointer register.

When bit 7 of the “fr” field is clear, the DPH/DPL register

is selected as the pointer register. This register is

accessed using the loadh and loadl instructions,

which load its high and low bytes, respectively. The upper

four bits of the DPH register are not used. Figure 4-4

shows indirect-with-offset addressing using the DPH/DPL

register as the pointer register.

Figure 4-4 Indirect-with-Offset Mode, Data Pointer

The following code example uses indirect-with-offset

addressing mode.

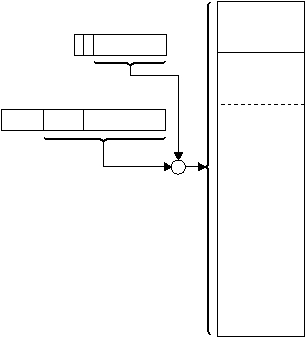

When bit 7 of the “fr” field is set, the SPH/SPL register is

selected as the pointer register. The upper four bits of the

SPH register are not used. Figure 4-5 shows indirect-with-

offset mode using the SPH/SPL register. In addition to this

indirect-with-offset addressing mode, there are also

push and pop instructions which automatically

increment and decrement the SPH/SPL register while

performing a data transfer between the top of stack and a

data memory location specified by the “fr” field. Stacks

grow down from higher addresses to lower addresses.

This stack addressing mechanism is completely

independent from the hardware stack used for subroutine

call and return.

When a pop instruction is used with the indirect-with-

offset addressing mode, the address calculation for the

“fr” operand is made using the value in the SPH/SPL

register before the automatic increment, even though the

stack operand itself is addressed using the value after the

automatic increment.

Figure 4-5 Indirect-with-Offset Mode, Stack Pointer

MyStuff= 0x038D

;define address MyStuff

loadh

MyStuff ;load the high byte of the

;DPH/DPL pointer register

;with 0x03

loadl

MyStuff ;load the low byte of the

;DPH/DPL pointer register

;with 0x8D

515-026a.eps

127

Special-Purpose

Registers

DPH Register

DPL Register

7

0

n

0

n

7

n n n n n n n

X

3

4

7

X X X n n n

0

9-Bit "fr" Field

from Instruction

1

8

0 m m m m m m m

0

+

7

6

3840 Bytes

Data Memory

128

Global Registers

mov

w,8(dp) ;load W with the contents of

;the memory location at

;effective address 0x038D

;(i.e. 0x0385 + 0x0008)

515-027a.eps

127

Special-Purpose

Registers

SPH Register

SPL Register

7

0

n

0

n

7

n n n n n n n

X

3

4

7

X X X n n n

0

9-Bit "fr" Field

from Instruction

1

8

1 m m m m m m m

0

+

7

6

3840 Bytes

Data Memory

128

Global Registers