IP2022 Data Sheet

www.ubicom.com

19

3.7

Interrupt Support

There are three types of interrupt sources:

•

On-Chip Peripherals–the serializer/deserializer units,

real-time timer, timer 0, timer 1, and timer 2 are capa-

ble of generating interrupts. The Parallel Slave Pe-

ripheral does not generate interrupts on its own; it

requires programming one of the Port B external inter-

rupt inputs to generate interrupts on its behalf.

•

External Interrupts–the eight pins on Port B can be

programmed to generate interrupts on either rising or

falling edges (see Section 5.1.1).

•

int Instruction–the int instruction can be executed

by software to generate an interrupt. The INT_EN bit

can be considered as the interrupt flag for the int in-

struction, if the ISR checks for interrupt source. The

INT_EN bit in the XCFG register must be set to en-

able the int instruction to trigger an interrupt. Be-

cause the reti instruction returns to the int

instruction, the INT_EN bit must be cleared in the in-

terrupt service routine (ISR) before returning.

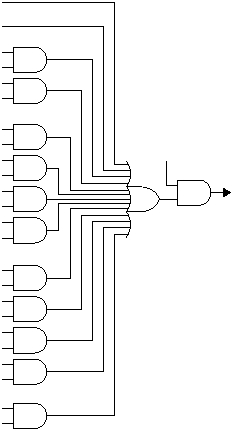

Figure 3-8 shows the system interrupt logic. Each

interrupt source has an interrupt enable bit. To be capable

of generating an interrupt, the interrupt enable bit and the

global interrupt enable (GIE) bit must be set.

Figure 3-8 System Interrupt Logic

3.7.1

Interrupt Processing

There is one interrupt vector held in the INTVECH and

INTVECL registers, which is reprogrammable by

software. When an interrupt is taken, the current PC is

saved in the IPCH and IPCL registers. On return from

interrupt (i.e. execution of the reti instruction), the PC is

restored from the IPCH and IPCL registers. Optionally, the

reti instruction may also copy the incremented PC to

the INTVECH and INTVECL registers before returning.

This has the effect of loading the INTVECH and INTVECL

registers with the address of the next instruction following

515-067.eps

Interrupt

to CPU

Port B Interrupt

Serializer/Deserializer Interrupt

Timer 0 Overflow Interrupt

T0IE Bit

Real-TIme Timer Interrupt

RTIE Bit

Timer 1 Compare Interrupt

T1CMP1IE Bit

Timer 1 Capture 1 Interrupt

T1CAP1TIE Bit

Timer 1 Compare/Capture 2 Interrupt

T1CMP2IE/T1CAP2IE Bit

Timer 1 Overflow Interrupt

T1OFIE Bit

Timer 2 Compare 1 Interrupt

T2CMP1IE Bit

int Instruction

GIE Bit

Timer 2 Capture 1 Interrupt

T2CAP1IE Bit

Timer 2 Compare/Capture 2 Interrupt

T2CMP2IE/T2CAP2IE Bit

Timer 2 Overflow Interrupt

T2OFIE Bit

INT_EN Bit