100

www.ubicom.com

IP2022 Data Sheet

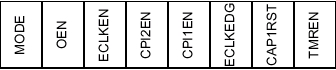

7.1.23 TxCFG1L Register

Timer 1 and 2 configuration.

7

6

5

4

3

2

1

0

Name

Description

MODE

Timer mode select

0 = PWM/timer mode

1 = Capture/compare mode

OEN

TxOUT enable bit

0 = TxOUT disabled. Port pin avail-

able for general-purpose I/O.

1 = TxOUT enabled. Port pin must

be configured for output in cor-

responding RxDIR register bit.

ECLKEN

TxCLK enable bit

0 = TxCLK disabled. Port pin avail-

able for general-purpose I/O.

1 = TxCLK enabled as clock

source for timer. Enabling this

bit does not make any other

restrictions on the use of the

TxCLK port pin for general-pur-

pose I/O.

CPI2EN

TxCPI2 enable bit

0 = System clock enabled as clock

source for timer. TxCPI2 port

pin available for general-pur-

pose I/O.

1 = TxCLK enabled as clock

source for timer. Enabling this

bit does not make any other

restrictions on the use of the

port pin for general-purpose

I/O.

CPI1EN

TxCPI1 enable bit

0 = Capture 1 input disabled.

TxCPI1 port pin available for

general-purpose I/O.

1 = TxCPI1 enabled as capture 1

input. Enabling this bit does not

make any other restrictions on

the use of the port pin for gen-

eral-purpose I/O.

ECLKEDG TxCLK edge sensitivity select. (This bit is

ignored if the ECLKEN bit is clear.)

0 = TxCLK increments timer on ris-

ing edge

1 = TxCLK increments timer on fall-

ing edge

CAP1RST

Reset timer on capture 1 event enable bit

0 = Timer value unchanged by

occurrence of a capture 1

event

1 = Timer value cleared by occur-

rence of a capture 1 event

TMREN

Timer enable bit

0 = Timer disabled. Timer clock

source shut off to reduce power

consumption.

1 = Timer enabled

Name

Description