PRELIMINARY

October 19, 2001

www.ubicom.com

1

1.0 Product Highlights

The Ubicom IP2022 Internet Processor™ combines

support for communication physical layer, Internet

protocol stack, device-specific application, and device-

specific peripheral software modules in a single chip, and

is reconfigurable over the Internet. It can be programmed,

and reprogrammed, using pre-built software modules and

configuration tools to create true single-chip solutions for

a wide range of device-to-device and device-to-human

communication applications. High speed communication

interfaces

are

available

via

on-chip

hardware

Serializer/Deserializer (SerDes) blocks. These two full-

duplex blocks allow the IP2022 to be used in a variety of

communication bridging applications. Each SerDes block

is capable of supporting 10Base-T Ethernet (MAC and

PHY), USB, GPSI, SPI, or UART. The 120 MHz operating

frequency, with most instructions executing in a single

cycle, delivers the throughput needed for emerging

network connectivity applications, and a flash-based

program memory allows both in-system and runtime

reprogramming. The IP2022 implements most peripheral,

communications and control functions via software

modules (ipModule™ software), replacing traditional

hardware for maximum system design flexibility. This

approach allows rapid, inexpensive product design and,

when needed, quick and easy reconfiguration to

accommodate changes in market needs or industry

standards.

Key Features:

• Designed to support single-chip networked solutions

• Fast processor core

• 64kB Flash program memory

• 20kB SRAM data/program memory

• Two SerDes communication blocks supporting com-

mon PHYs (Ethernet, USB, UARTs, etc.) and bridging

applications

• Advanced 120 MIPS RISC processor

• High speed packet processing

• Instruction set optimized for communication functions

•Supports software implementation of traditional hard-

ware functions

• In-system reprogrammable for highest flexibility

• Run time self-programmable

• Vpp = Vcc supply voltage

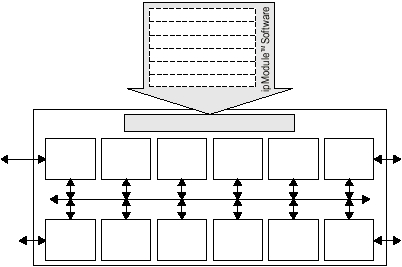

Figure 1-1 IP2022 Block Diagram

515-063.eps

IP2022

10Base-T Ethernet

USB 1.1

GPSI

SPI

UART/Modem

Bluetooth HCI

Customer Application

HTTP/SMTP/TFTP

TCP/UDP

IP/ICMP

Network Access Layer

PHY Firmware

ipOS Operating System

High-Speed

Serial Unit 2

(SERDES)

ISP/ISD

Interface

8-Input

10-Bit

A/DC

PLL

Clock

Multiplier

5

Timers

High-Speed

Serial Unit 1

(SERDES)

General

Purpose

I/O Ports

4-Kbyte

Data

RAM

16-Kbyte

Inst./Data

RAM

64-Kbyte

Flash

Memory

Internet

Processor

CPU

8/16-Bit

Parallel

Slave Port

ISA

I2C

General-Purpose I/O

Choices for

Communication:

10Base-T

Ethernet

USB 1.1

GPSI

SPI

UART/Modem

Bluetooth HCI

Host Bus

Choices for

Communication:

IP2022 Internet Processor™

Features and Performance Optimized for Network Connectivity