92

www.ubicom.com

IP2022 Data Sheet

7.3

Register Bit Definitions

For those registers which have special functions assigned

to bits or fields within the register, the definition of those

bits and fields is described below. The registers are

presented alphabetically.

7.3.1

ADCCFG Register (A/D Converter

Configuration)

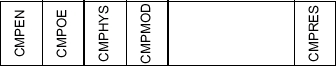

7.3.2

CMPCFG Register (Comparator Con-

figuration)

7

6

5

4

3

2

0

ADCREF

ADCJST

Rsrvd. ADCGO

ADCS2:0

Name

Description

ADCREF

A/D converter reference voltage select

0 = AVdd is the reference voltage

1 = RG3 port pin is used to receive

an external reference voltage

ADCJST

A/D converter result justification mode

select

00 = Right justified

01 = Signed

10 = Left justified

11 = Reserved

ADCGO

A/D converter GO/DONE bit

0 = When the last conversion has

completed, this bit reads as 0.

1 = Write 1 to begin a new conver-

sion. While the conversion is in

progress, this bit reads as 1.

ADCS2:0

A/D converter input channel select

000 = Port pin RG0

001 = Port pin RG1

010 = Port pin RG2

011 = Port pin RG3

100 = Port pin RG4

101 = Port pin RG5

110 = Port pin RG6

111 = Port pin RG7

7

6

5

4

3

1

0

Reserved

Name

Description

CMPEN

Comparator enable bit

0 = Comparator disabled

1 = Comparator enabled

CMPOE

Comparator output enable bit

0 = Comparator output disabled.

1 = Comparator output enabled on

port pin RG0.

CMPHYS

Comparator hysteresis enable bit

0 = Hysteresis disabled

1 = Hysteresis enabled

CMPMOD

Comparator mode bit

0 = Normal mode

1 = Squelch or comparator mode

for Ethernet

CMPRES

Comparator result (read-only)

0 = RG2 voltage > RG1

1 = RG1 voltage > RG2