IP2022 Data Sheet

www.ubicom.com

63

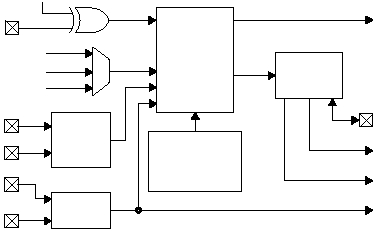

Figure 5-12 Clock/Data Separation and EOP Detection

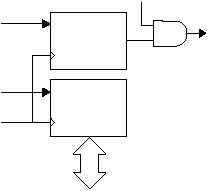

Figure 5-13 shows the receive data paths. Software

prepares a SERDES unit to receive data by programming

the receive shift count register (SxRCNT) and the clock

select bits in the SxMODE register appropriately for the

selected protocol. The SxRCNT register is copied to an

internal counter, and when that number of bits of data has

been received, the received data is loaded into the

SxRBUF register.

Figure 5-13 Receive Data Paths

In 10Base-T, GPSI, or USB mode, when an EOP is

detected the SxRCNT register is loaded with the number

of bits actually received, the EOP bit of the SxINTF

register is set, and the data bits are loaded into the

SxRBUF register. The RXBF bit in the SxINTE register

can be set to enable an interrupt on this event.

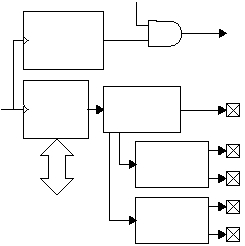

Figure 5-14 shows the transmit data paths. The SxTXP

and SxTXM pins correspond to the differential outputs of

the USB or Ethernet bus. Other serial protocols require

only one output pin, which is SxTXP by default.

Figure 5-14 Transmit Data Paths

515-003.eps

Clock/Data

Separation

and

Start

Condition

Detection

Receive Polarity

Reversal Bit

SxCLK

Receive

Clock

Receive

Data

Transmit

Clock

Clock

Data

EOP

UART Clock

Divider

EOP

Detection

Synchronization

Pattern

Register

(SxRSYNC)

SxRXP

Input

SxRXD

Input

Serial PLL Clock

OSC Clock

RTCLK

SxRXM

Input

Ethernet

Squelch

Circuit

SxRx+

SxRx-

515-004.eps

EOP

Receive

Count

Register

(SxRCNT)

Receive

Data

Receive

Clock

Receive

Buffer

Register

(SxRBUF)

Data Bus

RXBF

Receive

Interrupt

515-018.eps

Transmit

Configuration

Register

(SxTCFG)

Transmit

Clock

SxOE

Data

Encoder

Transmit

Buffer

Register

(SxTBUF)

Data Bus

SxTXPE

Pre-Emphasis

EOP

Generator

SxTXME

SxTXP

SxTXM

TXBE, TXEOP

Transmit

Interrupt