IP2022 Data Sheet

www.ubicom.com

61

5.5

Watchdog Timer

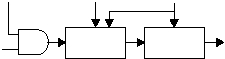

A Watchdog Timer is available for recovering from

unexpected system hangups. When the Watchdog Timer

is enabled, software must periodically clear the timer by

executing a cwdt instruction. Otherwise, the timer will

overflow, which resets the IP2022 and sets the WD bit in

the STATUS register. Any other source of reset clears the

WD bit, so software can use this bit to identify a reset

caused by the Watchdog Timer. The Watchdog Timer is

shown in Figure 5-11.

Figure 5-11 Watchdog Timer

The Watchdog Timer is enabled by setting the WDTE bit

in the FUSE1 register. The time period between reset or

clearing the timer and timer overflow is controlled by the

WDPS2:0 bits in the FUSE1 register, as shown in Table 5-

6.

The Watchdog Timer register is not visible to software.

The only feature of the Watchdog Timer visible to software

is the WD bit in the STATUS register.

5.6

Serializer/Deserializer (SERDES)

There are two SERDES units in the IP2022, which support

a variety of serial communication protocols, including

GPSI, SPI, UART, USB, and 10Base-T Ethernet. By

performing data serialization/deserialization in hardware,

the

CPU

bandwidth

needed

to

support

serial

communication is greatly reduced, especially at high baud

rates. Providing two units allows easy implementation of

protocol conversion or bridging functions, such as a USB

to 10Base-T Ethernet bridge.

Each SERDES unit uses up to 8 external digital signals:

SxCLK, SxRXD, SxRXM, SxRXP, SxTXM, SxTXME,

SxTXP, and SxTXPE/SxOE. The signals for SERDES1

are multiplexed with the Port E pins, and the signals for

SERDES2 are multiplexed with the Port F pins. The port

direction bits must be set appropriately for each pin that is

used. The SxOE signal is multiplexed with the SxTXPE

signal. Not all signals are used in all protocol modes (see

Table 5-9 for details). In addition to the digital signals,

there are also two analog signals only used in 10Base-T

Ethernet mode: SxRX+ and SxRX-. Port pin usage is

shown in Table 5-7.

Table 5-6 Watchdog Timer Period

WDPS2:0 (FUSE1 register)

Period (ms)*

000

20

001

40

010

80

011

160

100

320

101

640

110

1280

111

2560

* Time periods are approximate

515-076.eps

8-Bit

Timer

Watchdog

Timer Reset

Prescaler

Internal

RC Clock

(15 kHz)

WDTE

WDPS 2:0

cwdt Instruction