IP2022 Data Sheet

www.ubicom.com

59

high 8 bits come from the value being written to the

TxCAP2H register. Software should write the TxCAP2L

register before writing the TxCAP2H register, because

writing to the TxCAP2H register is used as an indication

that a new compare value has been written. Writing to the

TxCAP2H register is required for the new compare value

to take effect. In PWM mode, the 16-bit number latched

into the internal compare register by writing to the

TxCAP2H register does not take effect until the end of the

current PWM cycle.

Reading the TxCAP2H or TxCAP2L registers returns the

previously written value regardless of whether the value

stored in these registers has been transferred to the

internal compare register by writing to the TxCAP2H

register.

In Capture/Compare mode, this register captures the

value of the counter/timer when the TxCPI2 input is

triggered. In this mode, this register is read-only.

Reading the TxCAP2L register returns the least-

significant 8 bits of an internal capture register and causes

the most-significant 8-bits to be latched into the TxCAP2H

register. This allows software to read the TxCAP2H

register later and still be assured of atomicity.

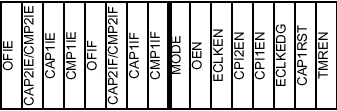

TxCFG1H/TxCFG1L Register

Selects timer operation mode, pin functions, interrupts

and other configuration settings.

•

OFIE—Timer overflow interrupt enable. Set to enable

timer overflow interrupts, clear to disable.

•

CAP2IE/CMP2IE—in PWM mode, compare 2 inter-

rupt enable. In Compare/Capture mode, capture 2 in-

terrupt enable.

•

CAP1IE—capture 1 interrupt enable.

•

CMP1IE—compare 1 interrupt enable.

•

OFIF—Timer overflow interrupt flag. Set on timer

overflow from 0xFFFF to 0x0000.

•

CAP2IF/CMP2IF—in PWM mode, set when the

counter/timer increments to the same value held in

the TxCMP2 register. In Compare/Capture mode, set

when the TxCPI2 input is triggered.

•

CAP1IF—set when the TxCPI1 input is triggered.

•

CMP1IF—in PWM mode, set when the counter/timer

is reset. In Compare/Capture mode, set when the

counter/timer is incremented to the same value held

in the TxCMP1 register.

•

MODE—set to select Compare/Capture mode,

cleared to select PWM or Timer mode.

•

OEN—TxOUT enable. Set to enable, clear to disable.

The port direction register bit for the corresponding

port pin must be programmed for output to enable this

output.

•

ECLKEN—enables the TxCLK input as a clock for the

counter/timer. Set to enable, clear to disable. Setting

this bit does not affect the use of the corresponding

port pin as a general-purpose input or output.

•

CPI2EN—enables the TxCAP2 register to be loaded

on a capture event. Set to enable, clear to disable.

Setting this bit does not affect the use of the corre-

sponding port pin as a general-purpose input or out-

put.

•

CPI1EN—enables the TxCAP1 register to be loaded

on a capture event. Set to enable, clear to disable.

Setting this bit does not affect the use of the corre-

sponding port pin as a general-purpose input or out-

put.

•

ECLKEDG—selects the sensitive edge for clocking

the counter/timer. Set for falling edges, clear for rising

edges.

•

CAP1RST—set to enable counter/timer reset on a

capture 1 input event, clear to disable reset.

•

TMREN—set to enable the counter, clear to disable.

When the counter/timer is disabled, clocking is inhib-

ited to minimize power consumption.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Figure 5-8 TxCFG1H/TxCFG1L Register