54

www.ubicom.com

IP2022 Data Sheet

as a high-impedance input. This prevents any false

signalling to external components which could occur if the

ports were allowed to assume a random configuration at

power-up.

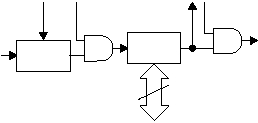

5.2

Timer 0

Timer 0 is an 8-bit timer intended to generate periodic

interrupts for ipModules that require being called at a

constant rate, such as UART and DTMF functions. This

use is supported in the instruction set by an option for the

reti instruction which adds the W register to the T0TMR

register when returning from an interrupt. Figure 5-3

shows the Timer 0 logic.

Figure 5-3 Timer 0 Block Diagram

The prescaler divisor is controlled by the T0PS3:0 bits of

the T0TMR register, as shown in Table 5-2.

Timer 0 is readable and writable as the T0TMR register.

The control and status register for Timer 0 is the T0CFG

register, as shown in Figure 5-4. Timer 0 should be

enabled before its interrupt is enabled.

•

T0EN—set to enable Timer 0, clear to disable. When

Timer 0 is disabled, clocking is inhibited to save pow-

er.

•

T0PS3:0—prescaler divisor, as described in Table 5-

2.

•

T0IE—set to enable Timer 0 overflow interrupts, clear

to disable interrupts.

•

T0IF—set on the occurrence of a Timer 0 overflow.

5.3

Real-Time Timer

The Real-Time Timer is an 8-bit timer intended to provide

a periodic system wake-up interrupt. Unlike the other

peripherals (except the Watchdog Timer and Port B

interrupts), the Real-Time Timer continues to function

when the system clock is disabled. For those applications

which spend much of their time with the OSC clock

oscillator turned off to conserve power, there are only

three available mechanisms for a wake-up: reset from the

Watchdog Timer, interrupt from a Port B input, and

interrupt from the Real-Time Timer. By using an interrupt

rather than reset, more of the CPU state is preserved and

some reset procedures such as initializing the port

direction registers can be skipped.

Figure 5-5 shows the Real-Time Timer logic.

Table 5-2 Prescaler Divisor

TOPS3:0

Divisor

0000

1

0001

2

0010

4

0011

8

0100

16

0101

32

0110

64

0111

128

1000

256

1001

Reserved

1010

Reserved

1011

Reserved

515-091.eps

T0TMR

Register

Data Bus

T0IE

T0IF

Timer 0

Interrupt

8-Bit

Prescaler

8

System

Clock

T0EN

T0PS 3:0

1100

Reserved

1101

Reserved

1110

Reserved

1111

Reserved

7

6

3

2

1

0

T0EN

T0PS3:0

Reserved T0IE

T0IF

Figure 5-4 T0CFG Register

Table 5-2 Prescaler Divisor (continued)

TOPS3:0

Divisor