IP2022 Data Sheet

www.ubicom.com

51

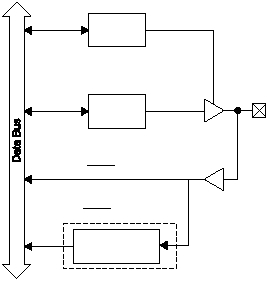

Figure 5-1 shows the internal hardware structure and

configuration registers for each pin of a port.

Figure 5-1 Port Pin Block Diagram

RD5

38

Parallel Slave Peripheral Data

RD6

39

Parallel Slave Peripheral Data

RD7

40

Parallel Slave Peripheral Data

RE0

41

Serial 1 Clock (S1CLK pin)

RE1

42

Serial 1 Receive Plus-Side Data (S1RXP

pin)

RE2

43

Serial 1 Receive Minus-Side Data

(S1RXM pin)

RE3

44

Serial 1 Receive Data (S1RXD pin)

RE4

45

Serial 1 Transmit Plus-Side Pre-Empha-

sis Data/Output Enable (S1TXPE/S1OE

pin)

RE5

46

High Power Output, Serial 1 Transmit

Plus-Side Data (S1TXP pin)

RE6

47

High Power Output, Serial 1 Transmit

Minus-Side Data (S1TXM pin)

RE7

48

Serial 1 Transmit Minus-Side Pre-Empha-

sis Data (S1TXME pin)

RF0

49

Serial 2 Transmit Plus-Side Pre-Empha-

sis Data/Output Enable (S2TXPE/S2OE

pin)

RF1

50

High Power Output, Serial 2 Transmit

Plus-Side Data (S2TXP pin)

RF2

51

High Power Output, Serial 2 Transmit

Minus-Side Data (S2TXM pin)

RF3

52

Serial 2 Transmit Minus-Side Pre-Empha-

sis Data (S2TXME pin)

RF4

57

Serial 2 Clock (S2CLK pin)

RF5

58

Serial 2 Receive Plus-Side Data (S2RXP

pin)

RF6

59

Serial 2 Receive Minus-Side Data

(S2RXM pin)

RF7

60

Serial 2 Receive Data (S2RXD pin)

RG0

61

ADC0 Input, Analog Comparator Output

RG1

62

ADC1 Input, Analog Comparator – Input

RG2

63

ADC2 Input, Analog Comparator + Input

RG3

64

ADC3 Input, ADC reference Input

RG4

66

ADC4 Input, SERDES1 Squelch – Input

Table 5-1 I/O Port Pin Alternate Functions (continued)

Name Pin

Alternate Function

RG5

67

ADC5 Input, SERDES1 Squelch + Input

RG6

68

ADC6 Input, SERDES2 Squelch – Input

RG7

69

ADC7 Input, SERDES2 Squelch + Input

Table 5-1 I/O Port Pin Alternate Functions (continued)

Name Pin

Alternate Function

515-030.eps

Port Pin

RxDIR

Register

RxIN Register

(SYNC bit set)

0 = Output

1 = Hi-Z Input

RxOUT

Register

Synchronization

Register

RxIN Register

(SYNC bit clear)