PRELIMINARY

May 27, 2001

www.ubicom.com

1

1.0

Product Overview

The Ubicom IP2022 Internet Processor™ combines

support for communication physical layer, Internet

protocol stack, device-specific application, and device-

specific peripheral software modules in a single chip, and

is reconfigurable over the Internet. It can be programmed,

and reprogrammed, using pre-built software modules and

configuration tools to create true single-chip solutions for

a wide range of device-to-device and device-to-human

communication applications. Fabricated in an advanced

0.25-micron process, its RISC-based deterministic

architecture provides high-speed computation, flexible I/O

control,

efficient

data

manipulation,

in-system

programming, and in-system debugging. A hardware

serializer/deserializer (SERDES) function gives the

IP2022 the ability to connect directly to a variety of

common network interfaces. This function provides the

ability to implement on-chip 10Base-T Ethernet (MAC and

PHY), USB, and a variety of other fast serial protocols.

Two SERDES units facilitate translation from one format

to another, allowing the IP2022 to be used as a protocol

converter. The 100 MHz operating frequency, with most

instructions executing in a single cycle, delivers the

throughput needed for emerging network connectivity

applications, and a flash-based program memory allows

both in-system and on-the-fly reprogramming. The

IP2022 implements peripheral, communications and

control functions as software modules (ipModule™

software), replacing traditional hardware for maximum

system design flexibility. This approach allows rapid,

inexpensive product design and, when needed, quick and

easy reconfiguration to accommodate changes in market

needs or industry standards.

On-chip dedicated hardware also includes a PLL, an 8-

channel 10-bit ADC, general-purpose timers, single-cycle

multiplier, analog comparator, LFSR units, external

memory interface, brown-out power voltage detector,

watchdog timer, low-power support, multi-source wakeup

capability, user-selectable clock modes, high-current

outputs, and 52 general-purpose I/O pins.

A TCP/IP network protocol stack is available, and a

variety of additional software that is necessary to form a

complete end-to-end connectivity solution is being

developed. Tools for developing with and using the

IP2022, including the complete Red Hat GNUPro tools,

are available from leading suppliers.

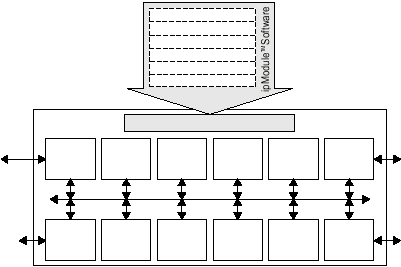

Figure 1-1 IP2022 Block Diagram

515-063.eps

IP2022

10Base-T Ethernet

USB 1.1

GPSI

SPI

UART/Modem

Bluetooth HCI

Customer Application

HTTP/SMTP/TFTP

TCP/UDP

IP/ICMP

Network Access Layer

PHY Firmware

ipOS Operating System

High-Speed

Serial Unit 2

(SERDES)

ISP/ISD

Interface

8-Input

10-Bit

A/DC

PLL

Clock

Multiplier

5

Timers

High-Speed

Serial Unit 1

(SERDES)

General

Purpose

I/O Ports

4-Kbyte

Data

RAM

16-Kbyte

Inst./Data

RAM

64-Kbyte

Flash

Memory

Internet

Processor

CPU

8/16-Bit

Parallel

Slave Port

ISA

I2C

General-Purpose I/O

Choices for

Communication:

10Base-T

Ethernet

USB 1.1

GPSI

SPI

UART/Modem

Bluetooth HCI

Host Bus

Choices for

Communication:

IP2022 Internet Processor™

Features and Performance Optimized for Network Connectivity