In-System Programming—IP2022 User’s Manual

370

www.ubicom.com

6.2.3

TRIM0 Register

6.2.4

FREQ Register

This register holds a 32-bit unsigned integer which represents the

OSC1 input frequency in Hz. Debugger/programmers can use this

number to calculate the values loaded into the flash configuration

register (FCFG) for device programming. The frequency is

specified from software using the FREQ assembler directive.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Description

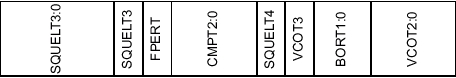

SQUELT5:0

SERDES squelch trim bits

FPERT

Controls flash block pulse erase time, for both self-program-

ming ferase and the FERASE command from the ISD/ISP

interface

0 = 20 ms

1 = 10 ms

CMPT2:0

Comparator offset trim bits

VCOT3:0

PLL VCO trim bits

BORT2:0

Brown-out detector bits