In-System Debugging—IP2022 User’s Manual

348

www.ubicom.com

5.5

ISD/ISP Interface

There are options in the implementation of an SPI bus. The

options chosen for the ISD/ISP interface are:

•

SPI Bus Slave—The IP2022 is an SPI bus slave. The device

programmer or debugging tool is the SPI bus master.

•

Clock Polarity and Phase Selection—The clock polarity and

phase options are chosen so that the clock signal is low when

it is not active, and negative edges of the clock are used to

output serial data.

•

Data Transfer Length—Data transfers are always 24 bits in

length.

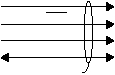

The SPI bus consists of four signal lines: TSI, TSO, TSCK, and

TSS. In addition, the ISD/ISP interface includes a reset signal

(TRST), power connections (DVdd, IOVdd), and an oscillator

clock input, as shown in Figure 5-7.

Figure 5-7 ISD/ISP Interface Signals

In-Circuit

Debugger

/Programmer

TRST

TSCK

TSS

TSI

TSO

SPI Bus

IP2022

515-046.eps

GND

DVdd, IOVdd

OSC