IP2022 User’s Manual—Peripherals

www.ubicom.com

321

4.11

External Memory Interface

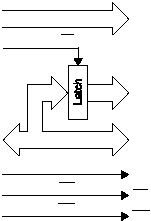

Port C and Port D can also be used for a parallel interface for up

to 128K bytes of external memory, as shown in Figure 4-18. Port

C implements the high address bits, and Port D is multiplexed

between data and the low address bits. A level-triggered 8-bit latch

(TI part number SN74AC573 or equivalent) is required for

demultiplexing.

Figure 4-18 External Memory Interface

External memory is accessed as 16-bit words at word-aligned byte

addresses 0x1000000 to 0x103FFFE, as shown in Figure 4-19.

External memory can only be accessed through the current

ADDRX/ADDRH/ADDRL pointer using the iread/ireadi and

IP2022

WR

External

Memory

515-087.eps

RD

A0

A8:1

A0

D7:0

LE

A16:9

RD

WR

Address

Data

Addr

RB6

RB7

RD7:0

RC7:0

RB5

RB4