IP2022 User’s Manual—Peripherals

www.ubicom.com

265

4.5

Watchdog Timer

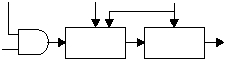

A Watchdog Timer is available for recovering from unexpected

system hangups. When the Watchdog Timer is enabled, software

must periodically clear the timer by executing a cwdt instruction.

Otherwise, the timer will overflow, which resets the IP2022 and

sets the WD bit in the STATUS register. Any other source of reset

clears the WD bit, so software can use this bit to identify a reset

caused by the Watchdog Timer. The Watchdog Timer is shown in

Figure 4-6.

Figure 4-6 Watchdog Timer

The Watchdog Timer is enabled by setting the WDTE bit in the

FUSE1 register. The time period between reset or clearing the

T2RST

Timer 2 reset bit. This bit always reads as zero.

0 = Writing 0 to this bit has no effect.

1 = Writing 1 to this bit clears Timer 2.

T1RST

Timer 1 reset bit. This bit always reads as zero.

0 = Writing 0 to this bit has no effect.

1 = Writing 1 to this bit clears Timer 1.

Name

Description

515-076.eps

8-Bit

Timer

Watchdog

Timer Reset

Prescaler

Internal

RC Clock

(15 kHz)

WDTE

WDPS 2:0

cwdt Instruction