IP2022 User’s Manual—Peripherals

www.ubicom.com

243

components which could occur if the ports were allowed to

assume a random configuration at power-up.

4.2

Timer 0

Timer 0 is an 8-bit timer intended to generate periodic interrupts

for ipModule software that requires being called at a constant rate,

such as UART and DTMF functions. This use is supported in the

instruction set by an option for the reti instruction which adds

the W register to the T0TMR register when returning from an

interrupt. For more information about the use of this option, see

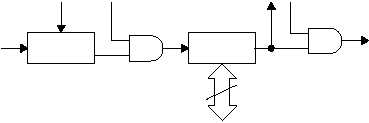

the Virtual Peripheral Guidelines document. Figure 4-3 shows the

Timer 0 logic.

Figure 4-3 Timer 0 Block Diagram

Timer 0 is readable and writable as the T0TMR register. The

control and status register for Timer 0 is the T0CFG register, as

described in Section 4.2.1. Timer 0 should be enabled before its

interrupt is enabled.

515-014.eps

T0TMR

Register

Data Bus

T0IE

T0IF

Timer 0

Interrupt

8-Bit

Prescaler

8

System

Clock

T0EN

T0PS 3:0