© 2000 Ubicom, Inc. All rights reserved.

- 1 -

www.ubicom.com

Ubicom™ and the Ubicom logo are trademarks of Ubicom, Inc.

I2C™ is a trademark of Philips Corporation

.

All other trademarks mentioned in this document are property of their respec-

tive companies.

PRELIMINARY

December 8, 2000

IP2022 Internet ProcessorTM

Features and Performance Optimized for Network Connectivity

1.0 PRODUCT OVERVIEW

1.1 Introduction

The Ubicom IP2022 Internet ProcessorTM combines sup-

port for communication physical layer, Internet protocol

stack, device-specific application and device-specific

peripheral software modules in a single chip, and is

reconfigurable over the Internet. It can be programmed,

and reprogrammed, using pre-built software modules

and configuration tools to create true single-chip solu-

tions for a wide range of device-to-device and device-to-

human communication applications. Fabricated in an

advanced 0.25-micron process, its RISC-based deter-

ministic architecture provides high-speed computation,

flexible I/O control, efficient data manipulation, in-system

programming, and in-system debugging. A hardware full-

duplex serializer/deserializer (SerDes) function gives the

IP2022 the ability to directly connect to a variety of com-

mon network interfaces. This function provides the ability

to implement on-chip 10BaseT Ethernet (MAC and PHY),

USB, and a variety of other fast serial protocols. The

inclusion of two SerDes units facilitate translation from

one format to another, allowing the IP2022 to be used as

a protocol converter. The 100 MHz operating frequency,

with most instructions executing in a single cycle, deliv-

ers the throughput needed for emerging network connec-

tivity applications, and a flash-based program memory

allows both in-system and on-the-fly reprogramming. The

IP2022 implements peripheral, communications and con-

trol functions as software modules (ipModules™), replac-

ing traditional hardware for maximum system design

flexibility. This approach allows rapid, inexpensive prod-

uct design and, when needed, quick and easy reconfigu-

ration to accommodate changes in market needs or

industry standards.

On-chip dedicated hardware also includes a PLL, an 8-

channel 10-bit ADC, general-purpose timers, single-cycle

multiply instruction, analog comparator, user-selectable

multi-level brown-out detector, watchdog timer, low-

power support, multi-source wakeup capability, user-

selectable clock modes, high-current outputs, and 52

general-purpose I/O pins.

A TCP/IP network protocol stack is available, and a vari-

ety of additional software that is necessary to form a

complete end-to-end connectivity solution is being devel-

oped. Tools for developing with and using the IP2022,

including the complete Red Hat GNUPro tools, are avail-

able from leading suppliers.

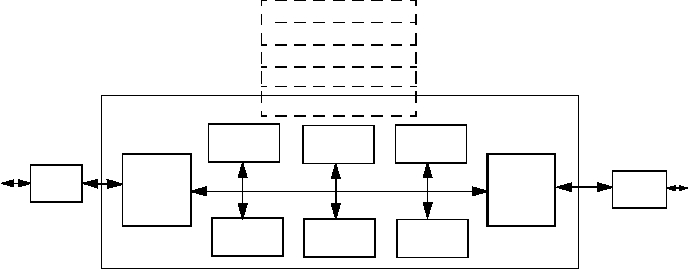

Figure 1-1. IP2022 Block Diagram

SerDes

I

SerDes

II

Core

Flash

RAM

Timer

PLL

A

DC

IP2022

Customer Application

HTTP

TCP

IP/ICMP

Network Access Layer

Trans-

ceiver

For Bridging

(optional)

Trans-

ceiver

10BaseT

USB

GPSI

SPI

UART

I2C

Etc.