1

Rev 2.2

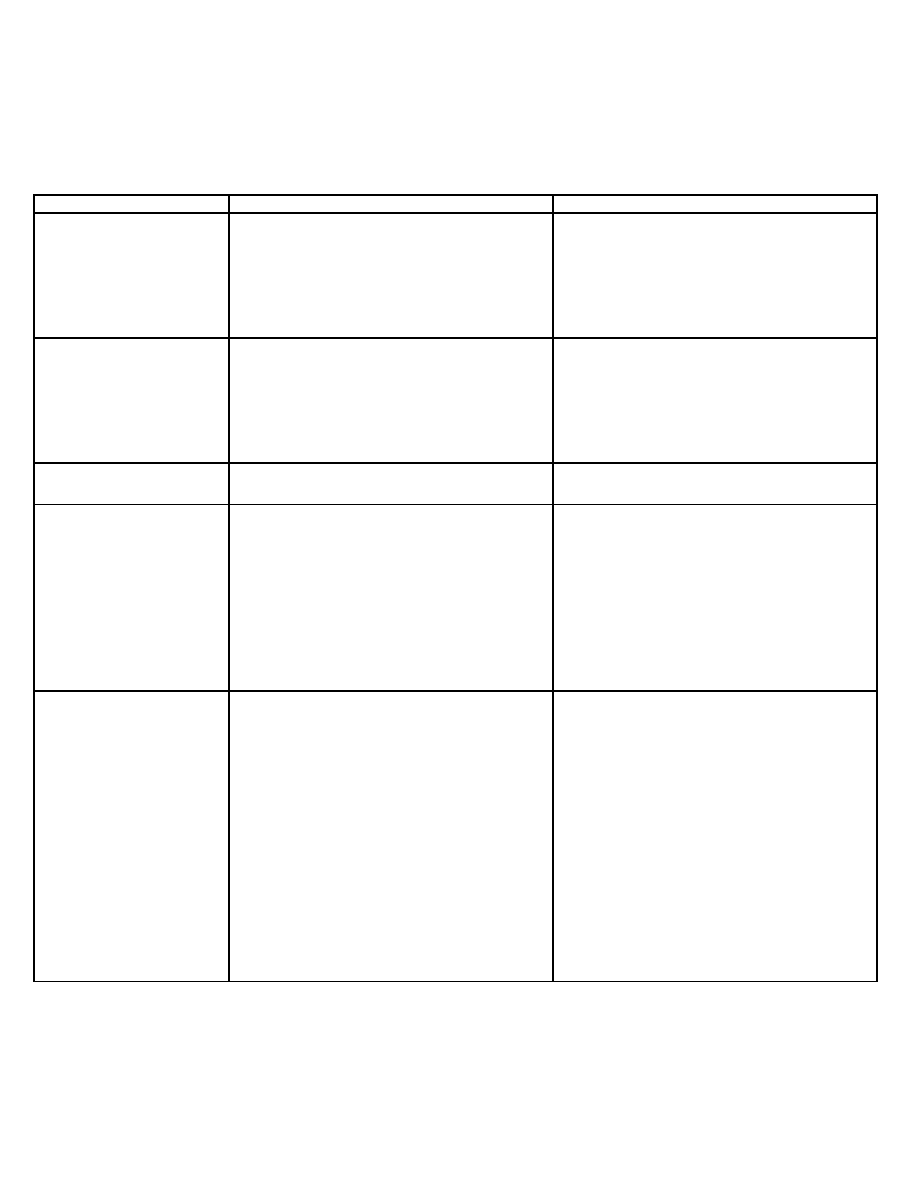

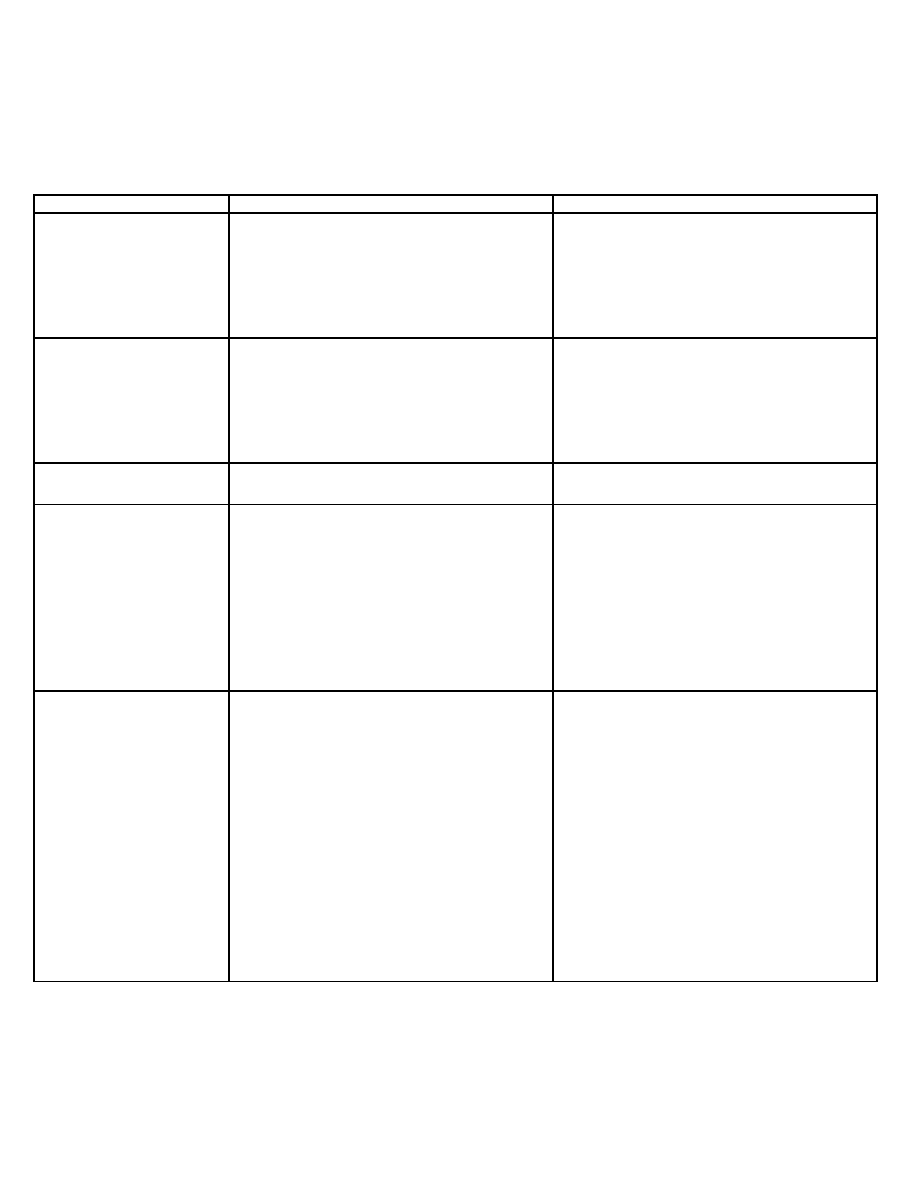

Summary of Differences Between

SX18/20/28 and SX48/52BD Production Release

SX18/20/28AC

SX48/52BD

Compatibility

Features

User selectable clock to instruction

ratio of 1:1 or 1:4.

User able to extend OPTION register

to use all 8-bits (extra features)

User able to extend stack size to 8-

levels.

Clock to instruction ratio locked at 1:1.

OPTION register fixed at 8-bit length.

Stack size fixed at 8-levels.

Port Read

When read is performed from a bit

position for a port, the operation is

actually reading the voltage level on

the pin itself.

Reading from a data register reads

either the voltage level of the

corresponding port pin or the data

contained in the port data register

depending on the status of PORTRD

bit contained in the T2CNTB register.

Port Registers

Ports A/B/C LVL, PLP, and Direction

registers are write only.

Ports A/B/C/D/E LVL, PLP, and

Direction registers are read/write.

MODE Register

MODE register controls access to the

port configuration registers. Bit 4 of

the MODE register is not used and is

initialized to 0.

MODE register not only controls

access to the port configuration

registers but also allows access to

Timer T1 and Timer T2 registers. It

also allows write operation to port

configuration and timer registers. Bit 4

is used to perform read or write

operation to configuration/status

registers.

FUSE Word

Register

Bits 11 used for selection of clock to

instruction ratio.

Bit 10 used for Synchronous input

enable.

Bit 7 used for Internal RC Oscillator

enable.

Bit 6 used to enable Internal Feedback

Resistor

Bits 5 and 6 used for Internal Oscillator

divider selection.

Bit 3 used for Code Protection enable.

Bit 2 used enable Watchdog Timer.

Bits 0,1 and 5 used for External

Oscillator Gain selection.

All bits the same with the exception of:

Bit 11 is unused.