© 2005 Ubicom, Inc. All rights reserved.

- 5 -

www.ubicom.com

SX20AC/SX28AC

2.0 CONNECTION DIAGRAMS

2.1 Pin Assignments

2.2 Pin Descriptions

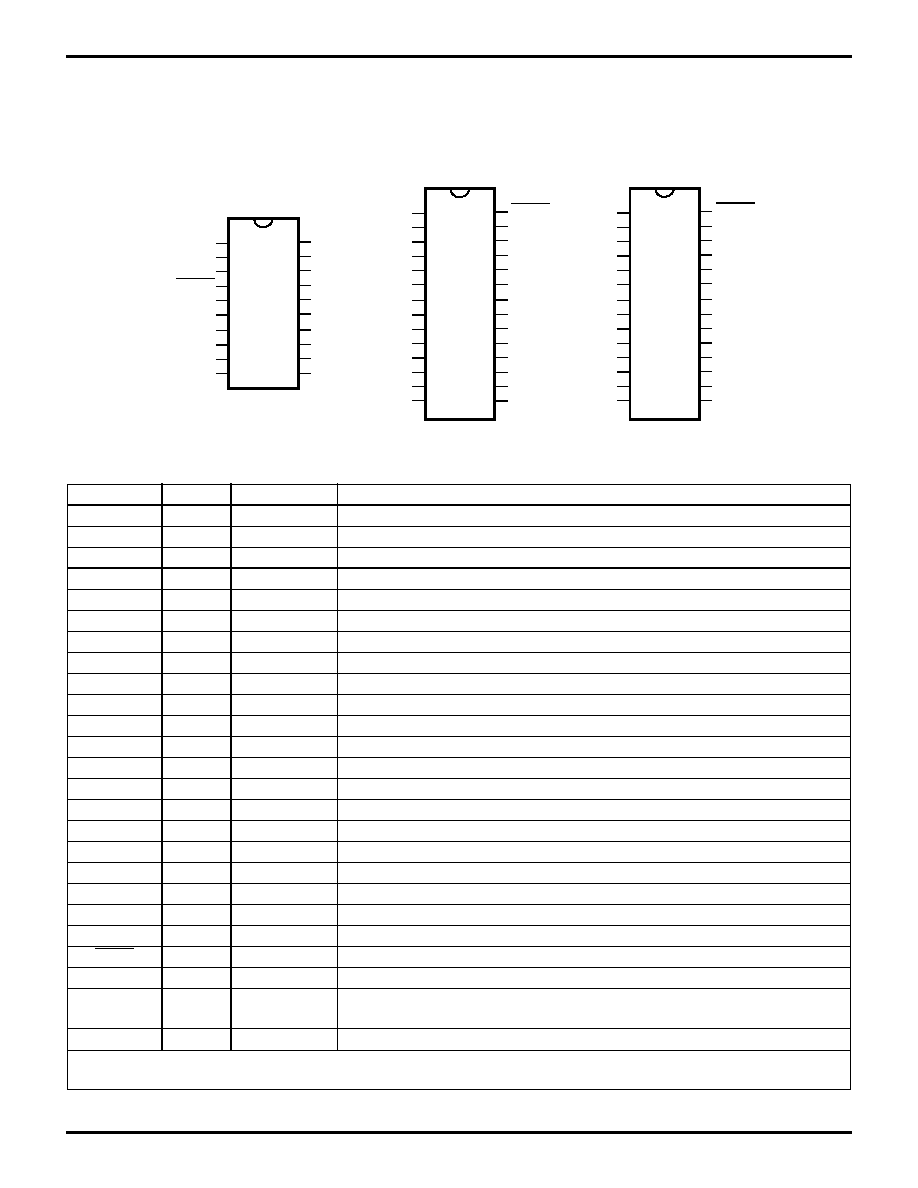

SSOP

1

2

3

4

5

6

7

8

16

15

RC4

RC3

RB6

RB5

SX28AC/SS

OSC2

RC7

RC6

RC5

V

dd

V

dd

RA2

RA3

RB0

RB1

RB2

RB3

RB4

Vss

MCLR

OSC1

RC2

RC1

RC0

RB7

9

10

11

12

13

14

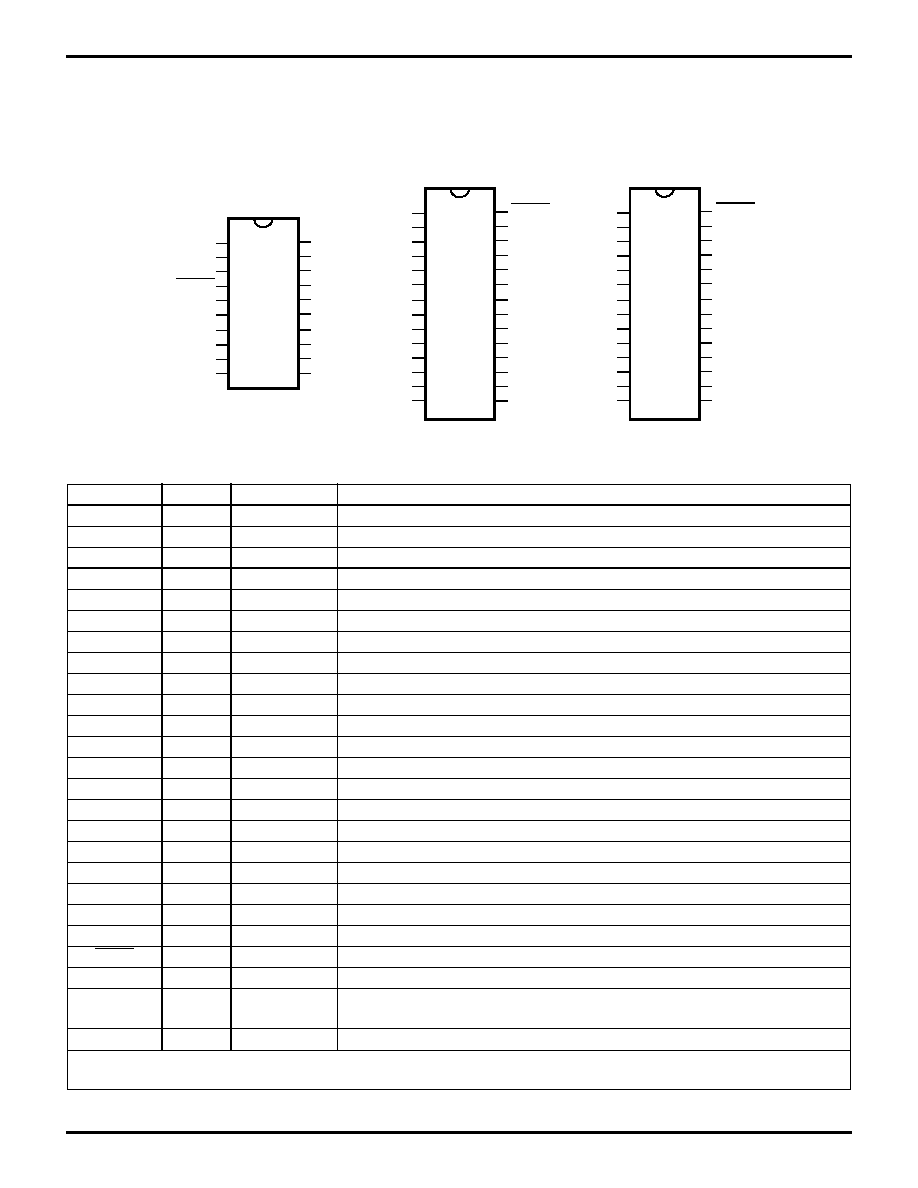

28

27

26

25

24

23

22

21

20

19

18

17

Vss

RTCC

RA0

RA1

1

2

3

4

5

6

7

8

16

15

RC4

RC3

RB6

RB5

SX28AC/DP

OSC2

RC7

RC6

RC5

n.c.

Vss

RA2

RA3

RB0

RB1

RB2

RB3

RB4

MCLR

OSC1

RC2

RC1

RC0

RB7

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

RTCC

V

dd

RA0

RA1

n.c.

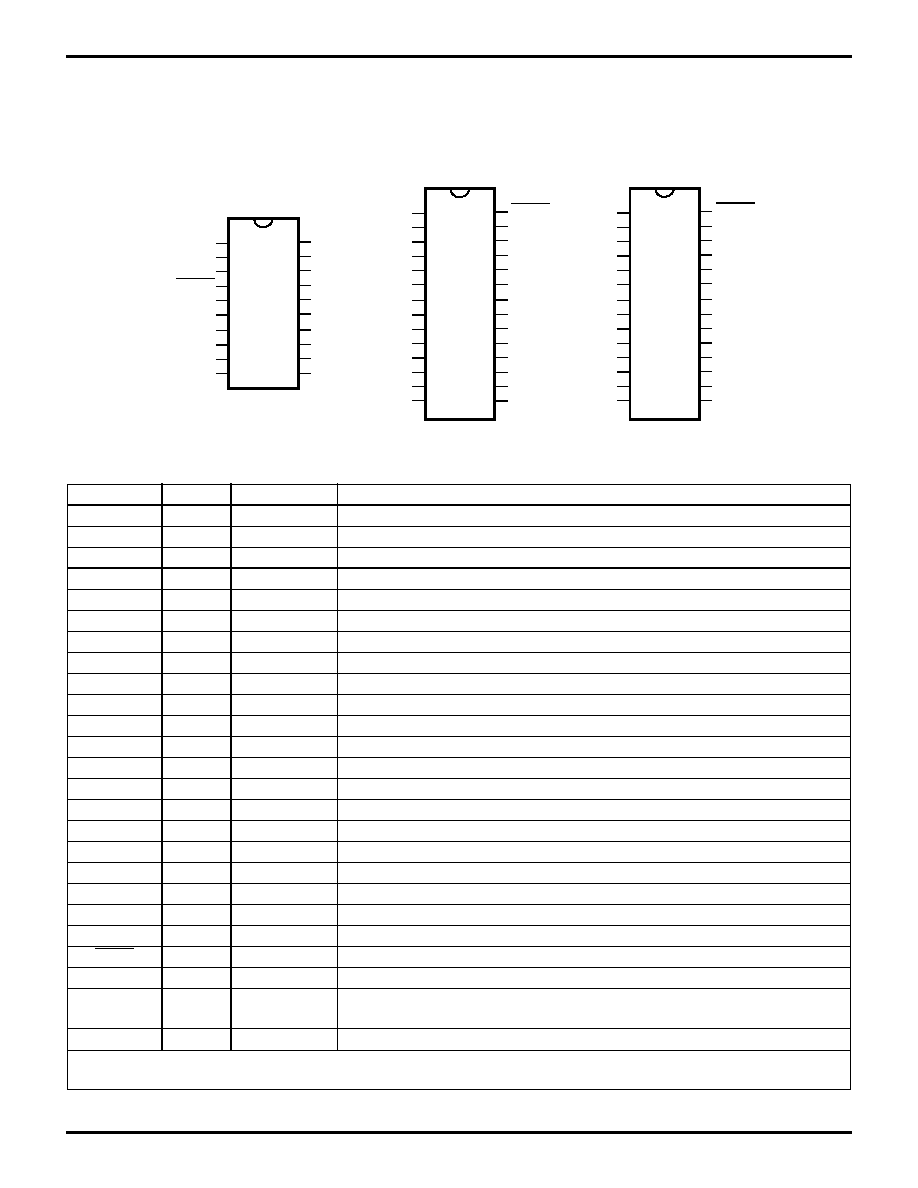

DIP

1

2

3

4

5

6

7

8

16

15

RB5

RB4

SX20AC/SS

OSC2

RTCC

RA0

RB0

RB1

RB2

RB3

MCLR

OSC1

V

dd

V

dd

RB7

RB6

9

10

14

13

12

11

20

19

18

17

RA2

RA3

Vss

RA1

Vss

SSOP

& SX28AC/SSU

Name

Pin Type Input Levels

Description

RA0

I/O

TTL/CMOS

Bidirectional I/O Pin; symmetrical source / sink capability

RA1

I/O

TTL/CMOS

Bidirectional I/O Pin; symmetrical source / sink capability

RA2

I/O

TTL/CMOS

Bidirectional I/O Pin; symmetrical source / sink capability

RA3

I/O

TTL/CMOS

Bidirectional I/O Pin; symmetrical source / sink capability

RB0

I/O

TTL/CMOS/ST

Bidirectional I/O Pin; comparator output; MIWU/Interrupt input

RB1

I/O

TTL/CMOS/ST

Bidirectional I/O Pin; comparator negative input; MIWU/Interrupt input

RB2

I/O

TTL/CMOS/ST

Bidirectional I/O Pin; comparator positive input; MIWU/Interrupt input

RB3

I/O

TTL/CMOS/ST

Bidirectional I/O Pin; MIWU/Interrupt input

RB4

I/O

TTL/CMOS/ST

Bidirectional I/O Pin; MIWU/Interrupt input

RB5

I/O

TTL/CMOS/ST

Bidirectional I/O Pin; MIWU/Interrupt input

RB6

I/O

TTL/CMOS/ST

Bidirectional I/O Pin; MIWU/Interrupt input

RB7

I/O

TTL/CMOS/ST

Bidirectional I/O Pin; MIWU/Interrupt input

RC0

I/O

TTL/CMOS/ST

Bidirectional I/O pin

RC1

I/O

TTL/CMOS/ST

Bidirectional I/O pin

RC2

I/O

TTL/CMOS/ST

Bidirectional I/O pin

RC3

I/O

TTL/CMOS/ST

Bidirectional I/O pin

RC4

I/O

TTL/CMOS/ST

Bidirectional I/O pin

RC5

I/O

TTL/CMOS/ST

Bidirectional I/O pin

RC6

I/O

TTL/CMOS/ST

Bidirectional I/O pin

RC7

I/O

TTL/CMOS/ST

Bidirectional I/O pin

RTCC

I

ST

Input to Real-Time Clock/Counter

MCLR

I

ST

Master Clear reset input active low

OSC1

I

ST

Crystal oscillator input external clock source input

OSC2

O

CMOS

Crystal oscillator output in R/C mode, internally pulled to V

dd

through weak

pull-up

V

dd

P

Positive supply pin

Note: I = input, O = output, I/O = Input/Output, P = Power, TTL = TTL input, CMOS = CMOS input,

ST = Schmitt Trigger input, MIWU = Multi-Input Wakeup input