© 2005 Ubicom, Inc. All rights reserved.

- 38 -

www.ubicom.com

SX20AC/SX28AC

16.1 Equivalent Assembler Mnemonics

Some assemblers support additional instruction mne-

monics that are special cases of existing instructions or

alternative mnemonics for standard ones. For example,

an assembler might support the mnemonic "CLC" (clear

carry), which is interpreted the same as the instruction

"clrb $03.0" (clear bit 0 in the STATUS register). Some of

the commonly supported equivalent assembler mnemon-

ics are described in Table 16-2.

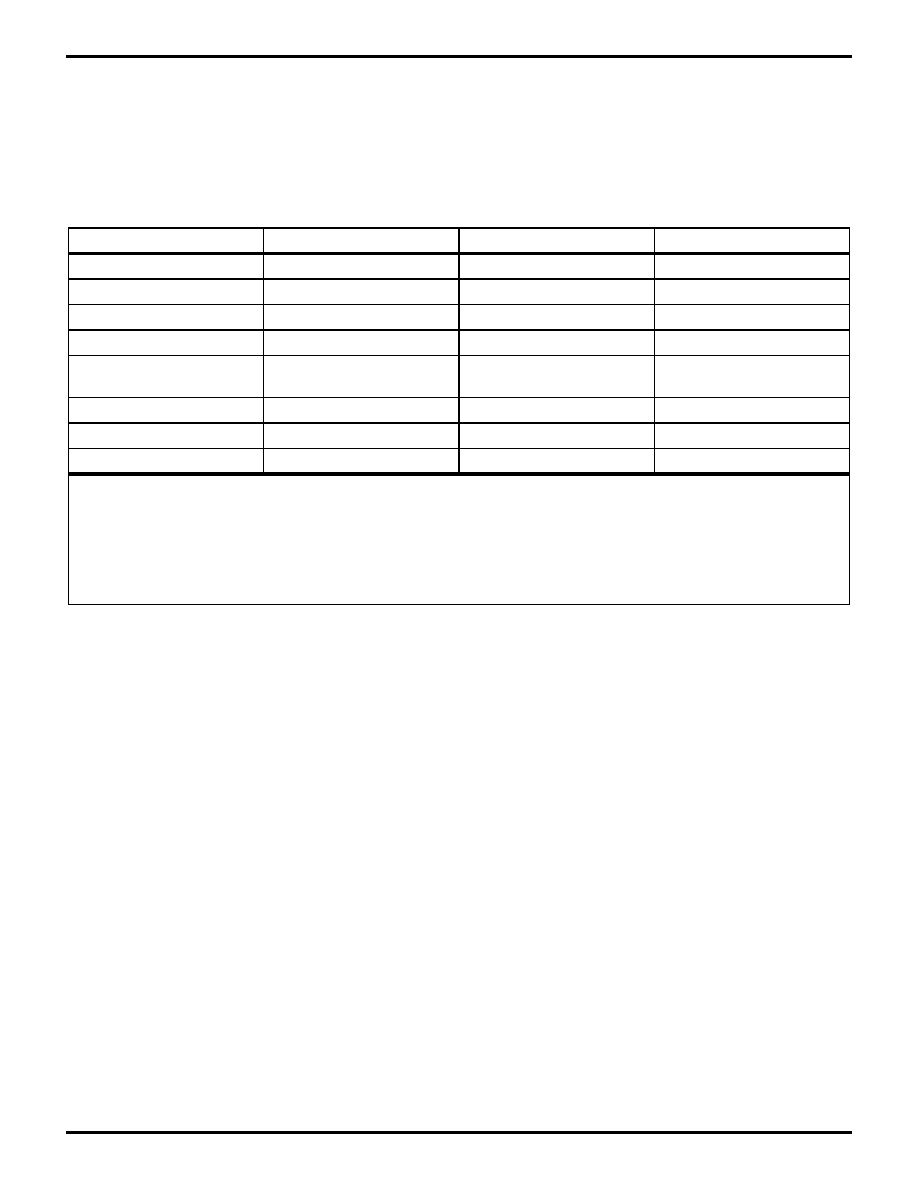

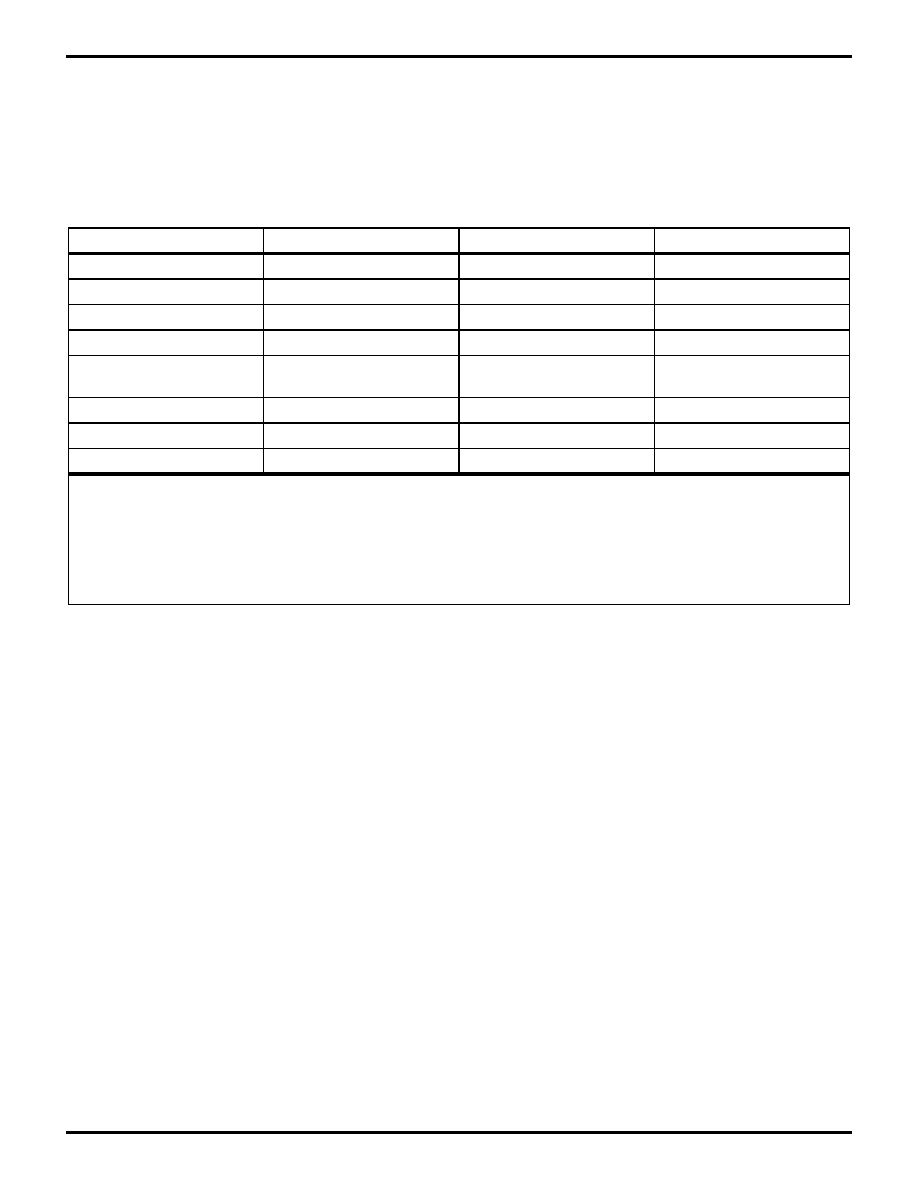

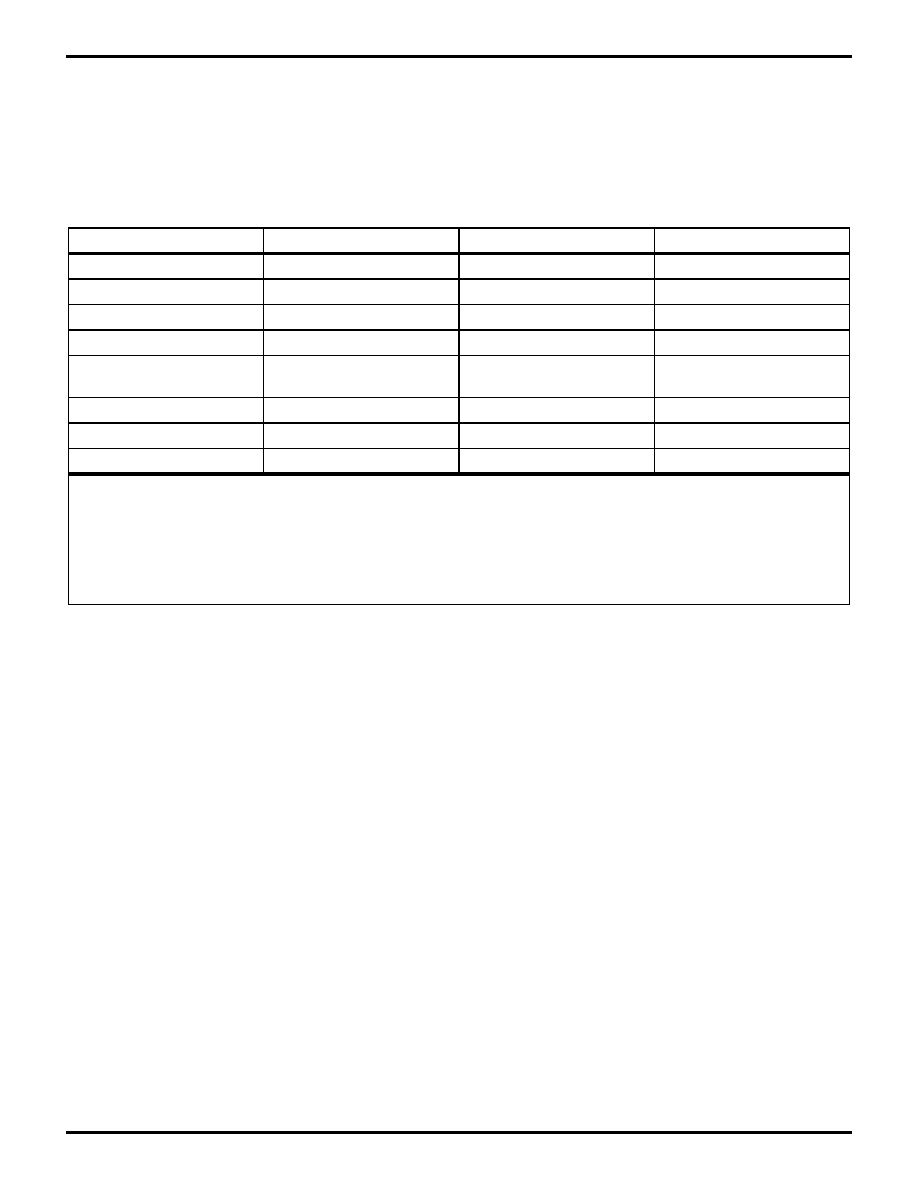

Table 16-2. Equivalent Assembler Mnemonics

Syntax

Description

Equivalent Cycles

CLC

Clear Carry bit

CLRB $03.0

1

CLZ

Clear Zero bit

CLRB $03.2

1

JMP W

Jump Indirect W

MOV $02,W

4 or 3 (note 1)

JMP PC+W

Jump Indirect W Relative

ADD $02,W

4 or 3 (note 1)

MODE imm4

Move Immediate to MODE

Register

MOV M,#lit

1

NOT W

Complement W

XOR W,#$FF

1

SC

Skip if Carry bit Set

SB $03.0

1 or 2 (note 2)

SKIP

Skip Next Instruction

SNB $02.0 or SB $02.0

4 or 2 (note 3)

Note 1: The JMP W or JMP PC+W instruction takes 4 cycles in the "compatible" clocking mode or 3 cycles in the

"turbo" clocking mode.

Note 2: The SC instruction takes 1 cycle if the tested condition is false or 2 cycles if the tested condition is true.

Note 3: The assembler converts the SKIP instruction into a SNB or SB instruction that tests the least significant bit

of the program counter, choosing SNB or SB so that the tested condition is always true. The instruction takes 4 cycles

in the "compatible" clocking mode or 2 cycles in the "turbo" clocking mode.