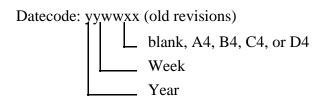

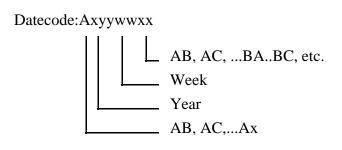

# New Revision of SX18/20/28AC (Datecode Axyywwxx)

Date: 5/18/99

# **Summary of Changes**

|                                                             | SX18/20/28AC Devices with<br>Datecode yywwxx (old rev)                                                                                                                            | SX18/20/28AC devices with<br>Datecode Axyywwxx (new rev)                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FUSE Word Register                                          | DIV2:DIV0 - Internal RC Oscillator<br>Divider: Bits DIV0, DIV1, and<br>DIV2 are located in bit locations 4,<br>5, and 6 respectively and provides a<br>selection of 8 frequencies | DIV1:DIV0 - Internal RC Oscillator<br>Divider: Bits DIV0, and DIV1 are<br>located in bit locations 5, and 6 respec-<br>tively and provides a selection of 4 fre-<br>quencies. Bit 4 is reserved.Bit DIV0 and<br>DIV1 also dual functions. DIV0<br>(FOSC2) extends the external oscillator<br>configuration. DIV1 (IFBD) is the inter-<br>nal feedback resistor disable bit for the<br>external resonator/crystal oscillator. |

|                                                             | OPTIONX - OPTION Register<br>Extension: Ability to disable pro-<br>grammability of bits 6 and 7 (RTW,<br>RTE_IE bits).                                                            | Moved to bit 7 of the FUSEX register.<br>The bit position is reserved.<br>Moved to bit 7 of the FUSEX register.<br>The bit position is reserved.                                                                                                                                                                                                                                                                             |

|                                                             | STACKX - Stack Extension: Limits<br>the stack size to two levels or<br>extends the size to 8 levels.                                                                              | The ort position is reserved.                                                                                                                                                                                                                                                                                                                                                                                                |

| FUSEX Word Register                                         | MEM1:MEM0 - Configure Program<br>Memory Size: Configures the pro-<br>gram memory size if desired to be<br>different than the factory setting.                                     | BP1:BP0 - These bits configure both the program memory size and the number of RAM banks. See the register map for details.                                                                                                                                                                                                                                                                                                   |

|                                                             | RAM1:RAM0 - Configure Number<br>of RAM Banks: Configures the<br>number of RAM banks if desired to<br>be different than the factory setting.                                       | The bit locations are used for trimming<br>the Brown-Out trip point (factory<br>untrimmed). The number of RAM<br>banks is selected through the BP1 and<br>BP0 bits.                                                                                                                                                                                                                                                          |

|                                                             | BOR1:BOR0 - Brown-Out Reset:<br>Can disable the Brown-Out feature<br>or enable and set the trip point to<br>4.2V.                                                                 | BOR1:BOR0 - Brown-Out Reset: Can<br>disable Brown -Out feature or enable<br>and select 3 different trip points.                                                                                                                                                                                                                                                                                                              |

| External Crystal/Resonator (LP,<br>XT, or HS Mode)          | The FOSC1:FOSC0 bits provide 3 settings.                                                                                                                                          | The FOSC2:FOSC0 bits provide 7 set-<br>tings.                                                                                                                                                                                                                                                                                                                                                                                |

| External Crystal/Resonator Oscil-<br>lator Component Values | Specified in the datasheet (latest version is dated 2/11/99)                                                                                                                      | The component values (Rf, C1, C2) values are different. Target values are available for reference.                                                                                                                                                                                                                                                                                                                           |

| Supply Voltage                                              | 4.5V to 6.25V                                                                                                                                                                     | 2.5V to 5.5V                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Parallel/Serial Prog. Times                                 | 100 ms/word                                                                                                                                                                       | < 50 ms/word                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Tools Support                                               | SX Key Rev E, Soft Rev 1.05                                                                                                                                                       | SX Key Rev E, Soft Rev 1.06                                                                                                                                                                                                                                                                                                                                                                                                  |

## **Device Configuration Options**

The register formats are shown in Figure 1 and the configuration fields within the registers are explained in Table 2 through Table 5. Note that the register formats vary, depending on the SX datecode variations.

#### FUSE Word for SX18/20/28AC Devices with Datecode yywwxx (old revisions)

| TURBO  | SYNC | OPTIONX | STACKX | IRC | DIV2 | DIV1 | DIV0 | CP | WDTE | FOSC1 | FOSC0 |

|--------|------|---------|--------|-----|------|------|------|----|------|-------|-------|

| Bit 11 |      |         |        |     |      |      |      |    |      |       | Bit 0 |

#### FUSE Word for SX18/20/28AC Devices with Datecode Axyywwxx (new revision)

| TURBO  | SYNC | Reserved | Reserved | IRC | DIV1/<br>IFBD | DIV0/<br>FOSC2 | Reserved | CP | WDTE | FOSC1 | FOSC0 |

|--------|------|----------|----------|-----|---------------|----------------|----------|----|------|-------|-------|

| Bit 11 |      |          |          |     |               |                |          |    |      |       | Bit 0 |

#### FUSEX Word for SX18/20/28AC Devices with Datecode yywwxx (old revisions)

| IRCTRI<br>M2 | PINS | IRCTRIM1 | IRCTRIM0 | Reserved | CF | BOR1 | BOR0 | RAM1 | RAM0 | MEM1 | MEM0  |

|--------------|------|----------|----------|----------|----|------|------|------|------|------|-------|

| Bit 11       |      |          |          |          |    |      |      |      |      |      | Bit 0 |

#### FUSEX Word for SX18/20/28AC Devices with Datecode Axyywwxx (new revision)

| IRCTRIM2      | PINS | IRCTRIM1 | IRCTRIM0 | OPTIONX/<br>STACKX | CF | BOR1 | BOR0 | BORTR<br>IM1 | BORTR<br>IM0 | BP1 | BP0   |

|---------------|------|----------|----------|--------------------|----|------|------|--------------|--------------|-----|-------|

| <b>Bit 11</b> |      |          |          |                    |    |      |      |              |              |     | Bit 0 |

Bit 11

#### **Figure 1 Device Configuration Register Formats**

### External Crystal/Resonator (XT, LP, or HS Mode)

SX18/20/28AC devices with datecode Axyywwxx (new revision) support extended crystal/resonator modes. Table 3 shows the different mode being supported. The new version of the device has improved internal crystal/resonator support circuitry. The external component values associated with oscillator circuit may have to chnage when using the new version. The oscillator circuit is currently being characterized. Contact Scenix for the component values.

# Table 2 FUSE Word Bits for SX18/20/28AC with Datecode yywwxx (old revisions)

| Option Bits     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TURBO           | Turbo Mode. Set to 1 for "compatible" mode, in which the instruction rate oper-<br>ates at one-fourth the oscillator clock rate. Set to 0 for the turbo mode, in which<br>the instruction rate is equal to the oscillator clock rate.                                                                                                                                                                                                                             |

| SYNC            | Synchronous Input Mode (for turbo mode operation). Set to 1 to disable or clear to 0 to enable synchronous inputs.                                                                                                                                                                                                                                                                                                                                                |

| OPTIONX         | OPTION Register Extension. Set to 1 to disable the programmability of bit 6 and bit 7 in the OPTION register, the RTW and RTE_IE bits (in other words, to force these two bits to 1). Clear to 0 to enable programming of the RTW and RTE_IE bits in the OPTION register.                                                                                                                                                                                         |

| STACKX          | Stack Extension. Set to 1 to limit the stack size to two locations. Clear to 0 to extend the stack size to eight locations.                                                                                                                                                                                                                                                                                                                                       |

| ĪRC             | Internal RC Oscillator. Set to 1 to disable the internal oscillator and have the OSC1 and OSC2 pins operate as defined by the FOSC1:FOSC0 bits. Clear to 0 to enable the internal oscillator, and to have the OSC1 pin floating and the OSC2 pin weakly pulled high.                                                                                                                                                                                              |

| DIV2:DIV0       | Internal RC Oscillator Divider. This field sets the divide-by factor for generating<br>the instruction clock from the internal oscillator when the internal oscillator is<br>enabled ( $\overline{IRC} = 0$ ). The nominal instruction rate is determined by DIV2:DIV0 as<br>follows:<br>000 = 4 MHz<br>001 = 2 MHz<br>010 = 1 MHz<br>011 = 500 kHz<br>100 = 250 kHz<br>101 = 125 kHz<br>110 = 62.5 kHz<br>111 = 31.25 kHz                                        |

| CP              | Code Protection. Set to 1 for no code protection. Clear to 0 for code protection.<br>With code protection, the program code and configuration registers read back as<br>scrambled data. This prevents reverse-engineering of your proprietary code and<br>configuration options.                                                                                                                                                                                  |

| WDTE            | Watchdog timer enable. Set to 1 to enable the Watchdog timer. Clear to 0 to disable the Watchdog timer.                                                                                                                                                                                                                                                                                                                                                           |

| FOSC1:<br>FOSC0 | External Oscillator Configuration. This field sets up the device to operate with a particular type of external oscillator when the device is configured to operate with an external oscillator ( $\overline{IRC} = 1$ ). The type of external oscillator is determined by FOSC1:FOSC0 as follows:<br>00 = LP - low-power crystal<br>01 = XT - normal crystal<br>10 = HS - high-speed crystal<br>11 = RC network - OSC2 is weakly pulled high and no CLKOUT output |

# Table 3 FUSE Word Bits for SX18/20/28AC with Datecode Axyywwxx (new revision)

| <b>Option Bits</b> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TURBO              | Turbo Mode. Set to 1 for "compatible" mode, in which the instruction rate oper-<br>ates at one-fourth the oscillator clock rate. Set to 0 for the turbo mode, in which<br>the instruction rate is equal to the oscillator clock rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SYNC               | Synchronous Input Mode (for turbo mode operation). Set to 1 to disable or clear to 0 to enable synchronous inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ĪRC                | Internal RC Oscillator. Set to 1 to disable the internal oscillator and have the OSC1 and OSC2 pins operate as defined by the FOSC1:FOSC0 bits. Clear to 0 to enable the internal oscillator, and to have the OSC1 pin floating and the OSC2 pin weakly pulled high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DIV1:DIV0          | Internal RC Oscillator Divider. This field sets the divide-by factor for generating<br>the instruction clock from the internal oscillator when the internal oscillator is<br>enabled ( $\overline{IRC} = 0$ ). The nominal instruction rate is determined by DIV1:DIV0 as<br>follows:<br>00 = 4 MHz<br>01 = 1 MHz<br>10 = 128 kHz<br>11 = 32 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ĪFBD               | Internal Feedback Disable. If $\overline{IRC} = 1$ , and $\overline{IFBD} = 1$ , the crystal/resonator oscillator can rely on the internal feedback resistor between the OSC1 and OSC2 pins.<br>If IFBD = 0, an external feedback resistor is required between the OSC1 and OSC2 pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <u>CP</u>          | Code Protection. Set to 1 for no code protection. Clear to 0 for code protection.<br>With code protection, the program code and configuration registers read back as<br>scrambled data. This prevents reverse-engineering of your proprietary code and<br>configuration options.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| WDTE               | Watchdog timer enable. Set to 1 to enable the Watchdog timer. Clear to 0 to disable the Watchdog timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FOSC2:<br>FOSC0    | External Oscillator Configuration. This combination of three register bits sets up<br>the device to operate with a particular type of external oscillator when the device<br>is configured to operate with an external oscillator ( $\overline{IRC} = 1$ ). Note that bit 5, the<br>DIV0/FOSC2 bit, operates as DIV0 with $\overline{IRC}=0$ , or as FOSC2 with $\overline{IRC}=1$ . The<br>type of external oscillator is determined by FOSC2:FOSC0 as follows:<br>000 = LP1 - low-power crystal (32 KHz)<br>001 = LP2 - low-power crystal (32 KHz to 1 MHz)<br>010 = XT1 - low-power crystal (32 KHz to 10 MHz)<br>011 = XT2 - normal crystal (1 MHz to 24 MHz)<br>100 = HS - normal crystal (1 MHZ to 50 MHz)<br>101 = Reserved<br>110 = Reserved<br>111 = External RC<br>Note: The frequency ranges have not been characterized. These are target values. |

| Table 4 FUSEX Bits for SX18/20/ | 28AC with Datecode | vvwwxx (old revisions) |

|---------------------------------|--------------------|------------------------|

|                                 |                    |                        |

| <b>Option Bits</b>    | Description                                                                                                                                                                                                                                                                                                                            |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRCTRIM2:<br>IRCTRIM0 | Internal RC Oscillator Trim. This 3-bit field adjusts the operation of the internal RC oscillator to make it operate within the target frequency range of 4.0 MHz plus or minus 8%. Parts are shipped from the factory untrimmed. The device relies on the programming tool to provide the trimming function.                          |

| CF                    | Carry Flag Input. Set to 1 to ignore the carry flag as an input to addition and sub-<br>traction operations. Clear to 0 to add the carry flag into all addition operations<br>(ADD fr,W means fr = fr + W + C); and to subtract the complement of the carry<br>flag from all subtraction operations (SUB fr,W means fr = fr - W - /C). |

| BOR1:<br>BOR0         | Brown-Out Reset. These two factory-configured bits should not be changed<br>unless you want to enable the brown-out functionality of the device. To enable<br>the brown-out feature (4.2V trip level), set these bits to 01. To disable the brown-<br>out feature set both bits to 1.                                                  |

| RAM1:<br>RAM0         | Configured Number of RAM Banks. These two factory-configured bits should<br>not be changed unless you want to reduce the configured amount of RAM in the<br>device. To do so, use one the following RAM1:RAM0 settings:<br>00 = 1 bank<br>01 = 2 banks<br>10 = 4 banks<br>11 = 8 banks (default)                                       |

| MEM1:<br>MEM0         | Configured Memory Size. These two factory-configured bits should not be<br>changed unless you want to reduce the configured amount of program memory in<br>the device. To do so, use one the following MEM1:MEM0 settings:<br>00 = 1 page<br>01 = 1 page<br>10 = 4 pages<br>11 = 8 pages (default)                                     |

# Table 5 FUSEX Bits for SX18/20/28AC with Datecode Axyywwxx (new revision)

| <b>Option Bits</b>    | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRCTRIM2:<br>IRCTRIM0 | Internal RC Oscillator Trim. This 3-bit field adjusts the operation of the internal RC oscillator to make it operate within the target frequency range of 4.0 MHz plus or minus 8%. Parts are shipped from the factory untrimmed. The device relies on the programming tool to provide the trimming function.                                                                                                      |

| OPTIONX/<br>STACKX    | OPTION Register Extension and Stack Extension. Set to 1 to disable the pro-<br>grammability of bit 6 and bit 7 in the OPTION register, the RTW and RTE_IE<br>bits (in other words, to force these two bits to 1); and to limit the program stack<br>size to two locations. Clear to 0 to enable programming of the RTW and RTE_IE<br>bits in the OPTION register, and to extend the stack size to eight locations. |

| CF                    | Carry Flag Input. Set to 1 to ignore the carry flag as an input to addition and sub-<br>traction operations. Clear to 0 to add the carry flag into all addition operations<br>(ADD fr,W means fr = fr + W + C); and to subtract the complement of the carry<br>flag from all subtraction operations (SUB fr,W means fr = fr - W - /C).                                                                             |

| BOR1:<br>BOR0         | Brown-Out Reset. The BOR1:BOR0 bits enable or disable the brown-out reset<br>function and set the brown-out threshold voltage as follows:<br>00 = 4.2V<br>01 = 2.6V<br>10 = 2.2V<br>11 = Disable Brown-Out Reset                                                                                                                                                                                                   |

| BORTRIM1:<br>BORTRIM0 | Brown-Out trim bits (parts are shipped out of the factory untrimmed).                                                                                                                                                                                                                                                                                                                                              |

| BP1:<br>BP0           | Configured Memory Size. These two factory-configured bits should not be<br>changed unless you want to reduce the configured amount of program memory in<br>the device. To do so, use one the following BP1:BP0 settings:<br>00 = 1 page, 1 bank<br>01 = 1 page, 2 banks<br>10 = 4 pages, 4 banks<br>11 = 4 pages, 8 banks (default)                                                                                |

### **DC Electrical Characteristics (Target Specs)**

SX18AC/SX20AC/SX28AC (Datecode Axyywwxx, new revision); Operating Temperature 0° C <= Ta <= +70° C (Commercial)

| Symbol                           | Parameter                                                                       | Conditions                                                                                                                            | Min                                      | Тур                      | Max                                   | Units                |

|----------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------|---------------------------------------|----------------------|

| $V_{dd}$                         | Supply Voltage                                                                  |                                                                                                                                       | 2.5                                      | -                        | 5.5                                   | V                    |

| V <sub>por</sub>                 | V <sub>dd</sub> start voltage to ensure<br>Power-On Reset                       |                                                                                                                                       | V <sub>ss</sub>                          | -                        | -                                     | V                    |

| S <sub>Vdd</sub>                 | V <sub>dd</sub> rise rate                                                       |                                                                                                                                       | 0.05                                     | -                        | -                                     | V/ms                 |

| I <sub>dd</sub>                  | Supply Current, active                                                          | $V_{dd} = 5.0V, F_{osc} = 50 \text{ MHz}$ $V_{dd} = 5.0V, F_{osc} = 4 \text{ MHz internal}$ $V_{dd} = 2.5V, F_{osc} = 20 \text{ MHz}$ | -                                        | 65<br>6<br>12            | -                                     | mA<br>mA<br>mA       |

| I <sub>pd</sub>                  | Supply Current, power down                                                      | $V_{dd}$ = 5.5V, WDT enabled<br>$V_{dd}$ = 5.5V, WDT disabled<br>$V_{dd}$ = 2.5V, WDT enabled<br>$V_{dd}$ = 2.5V, WDT disabled        | -                                        | TBD<br>1.0<br>TBD<br>500 | -                                     | μΑ<br>μΑ<br>μΑ<br>nA |

| V <sub>ih,</sub> V <sub>il</sub> | Input Levels<br>MCLR, OSC1, RTCC<br>Logic High<br>Logic Low<br>All Other Inputs |                                                                                                                                       | 0.8V <sub>dd</sub><br>V <sub>ss</sub>    |                          | V <sub>dd</sub><br>0.2V <sub>dd</sub> | V<br>V               |

|                                  | CMOS<br>Logic High<br>Logic Low<br>TTL                                          |                                                                                                                                       | 0.7V <sub>dd</sub><br>V <sub>ss</sub>    |                          | V <sub>dd</sub><br>0.3V <sub>dd</sub> | V<br>V               |

|                                  | Logic High<br>Logic Low                                                         |                                                                                                                                       | 2.0<br>V <sub>ss</sub>                   |                          | V <sub>dd</sub><br>0.8                | V<br>V               |

| l <sub>il</sub>                  | Input Leakage Current                                                           | $V_{in} = V_{dd} \text{ or } V_{ss}$                                                                                                  | -1.0                                     |                          | +1.0                                  | μA                   |

| I <sub>ip</sub>                  | Weak Pullup Current                                                             | $V_{dd} = 5.0V, V_{in} = 0V$ $V_{dd} = 2.5V, V_{in} = 0V$                                                                             |                                          |                          | 400<br>80                             | μΑ<br>μΑ             |

| V <sub>oh</sub>                  | Output High Voltage<br>OSC2, Ports B, C<br>Port A                               | Ioh = 20mA, Vdd = 4.5V<br>Ioh = 12mA, Vdd = 2.5V<br>Ioh = 30mA, Vdd = 4.5<br>Ioh = 18 mA, Vdd = 2.5V                                  | Vdd-0.7<br>Vdd-0.7<br>Vdd-0.7<br>Vdd-0.7 |                          |                                       | V<br>V<br>V<br>V     |

| V <sub>ol</sub>                  | Output Low Voltage<br>All Ports, OSC2                                           | Iol = 30mA, Vdd = 4.5V<br>Iol = 18mA, Vdd = 2.5V                                                                                      |                                          |                          | 0.6<br>0.6                            | V<br>V               |

### AC Electrical Characteristics (Target Specs)

SX18AC/20AC/28AC (Datecode Axyywwxx, new revision); Operating Temperature 0° C <= Ta <= +70° C (Commercial)

| Symbol                              | Parameter                         | Min   | Тур | Max   | Units | Conditions |

|-------------------------------------|-----------------------------------|-------|-----|-------|-------|------------|

| F <sub>osc</sub>                    | External CLKIN Frequency          | DC    | -   | 4.0   | MHz   | RC         |

|                                     |                                   |       |     | 10    | MHz   | XT1        |

|                                     |                                   |       |     | 24    | MHz   | XT2        |

|                                     |                                   |       |     | 50    | MHz   | HS         |

|                                     |                                   |       |     | 32    | KHz   | LP1        |

|                                     |                                   |       |     | 1.0   | MHz   | LP2        |

|                                     | Oscillator Frequency              | DC    | -   | 4.0   | MHz   | RC         |

|                                     |                                   | 0.032 |     | 10.0  | MHz   | XT1        |

|                                     |                                   | 1.0   |     | 24.0  | MHz   | XT2        |

|                                     |                                   | 1.0   |     | 50    | MHz   | HS         |

|                                     |                                   | DC    |     | 32    | KHz   | LP1        |

|                                     |                                   | 0.032 |     | 1.0   | MHz   | LP2        |

| T <sub>osc</sub>                    | External CLKIN Period             | 250   | -   | -     | ns    | RC         |

|                                     |                                   | 100   |     |       | ns    | XT1        |

|                                     |                                   | 41.7  |     |       | ns    | XT2        |

|                                     |                                   | 20    |     |       | ns    | HS         |

|                                     |                                   | 31.25 |     |       | μs    | LP1        |

|                                     |                                   | 1.0   |     |       | μs    | LP2        |

|                                     | Oscillator Period                 | 250   | -   | -     | ns    | RC         |

|                                     |                                   | 100   |     | 31.25 | μs    | XT1        |

|                                     |                                   | 41.7  |     | 1.0   | μs    | XT2        |

|                                     |                                   | 20    |     | 1.0   | μs    | HS         |

|                                     |                                   | 31.25 |     | -     | μs    | LP1        |

|                                     |                                   | 1.0   |     | 31.25 | μs    | LP2        |

| T <sub>osL</sub> , T <sub>osH</sub> | Clock in (OSC1) Low or High Time  | 50    | -   | -     | ns    | XT1/XT2    |

|                                     |                                   | 8.0   |     |       | ns    | HS         |

|                                     |                                   | 2.0   |     |       | μs    | LP1/LP2    |

| T <sub>osR</sub> , T <sub>osF</sub> | Clock in (OSC1) Rise or Fall Time | -     | -   | 25    | ns    | XT1/XT2    |

|                                     |                                   |       |     | 25    | ns    | HS         |

|                                     |                                   |       |     | 50    | μs    | LP1/LP2    |

Note:Data in the Typical ("TYP") column is at 5V, 25° C unless otherwise stated.

Internal RC Oscillator AC specs are still being characterized. Specification is  $4MHz \pm 8\%$  over commercial temp (0° C-70° C) range.

# Comparator DC and AC Specifications (Target Specs)

| Parameter                       | Conditions                    | Min | Тур    | Max       | Units |

|---------------------------------|-------------------------------|-----|--------|-----------|-------|

| Input Offset Voltage            | 0.4V < Vin < Vdd – 1.5V       |     | +/- 10 | +/- 25    | mV    |

| Input Common Mode Voltage Range |                               | 0.4 |        | Vcc – 1.3 | V     |

| Voltage Gain                    |                               |     | 300k   |           | V/V   |

| DC Supply Current (enabled)     | Vdd = 5.5V                    |     |        | 120       | μA    |

| Response Time                   | V <sub>overdrive</sub> = 25mV |     |        | 250       | ns    |