Application Note #:AN15 Stephen Holland Nov 1999

# SCENIX SX18/28AC to SX48/52BD Conversion

# 1.0 OVERVIEW

Although the SX18/28AC and SX48/52BD share the same basic architecture, there are numerous minor changes which the designer should be aware of. This document will help the designer to understand the differences between these variants of the SX family, and the software changes that may need to be implemented.

# 1.1 SX48/52 Modifications

The SX48/52 expands on the same basic architecture as the SX18/28, sharing an identical instruction set and feature set, with the following additional features and modifications:

- 4Kx 12 bits EE/Flash program memory rated for 10000 rewrite cycles

- 262 x 8 bits SRAM

- 5 8-bit ports on SX52; 1 4-bit, 4 8-bit ports on SX48

- Two 16-bit timers with 8-bit prescalers supporting:

- Software Timer mode

- PWM mode

- Simultaneous PWM/Capture mode

- External Event mode

- Port LVL, PLP, ST, and Direction registers are read/write

- RTCC interrupt flag

- Ability to disable clock during SLEEP mode

- Selectable delay reset timeout period (DRT)

Please consult the SX48/52 datasheet for more details on all the SX48/52 features.

Note: There are some additional features which will be made available in the production released revision of SX48/52. Please see section 3.0 for more details on these improvements.

# 1.2 Conversion

Almost all software written for the SX18/28 can be converted for use on the SX48/52 with only minor modifications. Please be advised that object code compiled specifically for the SX18/28 will not operate on the SX48/52, as the FUSE and FUSEX registers do not have a compatible arrangement.

Scenix<sup>™</sup> and the Scenix logo are trademarks of Scenix Semiconductor, Inc. I<sup>2</sup>C<sup>™</sup> is a trademark of Philips Corporation PIC® is a registered trademark of Microchip Technology, Inc.

# 1.3 MODE register

The MODE register value on the SX48/52 has been expanded to use 5 bits. This provided the additional address pointers to include read capability for the port ST, LVL, PLP, and direction registers. In the SX18/28, the MODE register address pointer only required 4 bits and the following instruction alone could be used to modify the MODE register:

mov M,#

With SX48/52 however, this instruction will not modify all 5 bits of the MODE register to correctly point to entire range of registers pointed to by MODE, as the mov M,# instruction only has a 4-bit operand. When all 5-bits of the MODE register need to be modified, the following instructions should instead be used:

mov W,# mov M,W

This will ensure that all 5-bits of the MODE address pointer are written.

# 1.4 Device Configuration Registers

The SX device has 2 registers (FUSE and FUSEX) that are used to configure various optional modes of operation.

The SX48/52 have different FUSE and FUSEX bit assignments from SX18/28. Depending on the assembler or tool used, the directives, device configuration or FUSE/FUSEX assignment will need to be modified. For this reason, all object targetted for SX18/28 will need to be re-compiled with SX48/52 as the target device.

Note: The FUSE and FUSEX assignment directives vary depending on the tool vendor, and assembler being used. Please consult your assembler software manual for details on the different directives for each SX device.

Microchip® is a registered trademark of Microchip Technology, Inc.

$<sup>\</sup>mathsf{SX}\text{-}\mathsf{Key}^{{}^{\mathsf{T}\!\mathsf{M}}}$  is a trademark of Parallax, Inc.

Microwire<sup>™</sup> is a trademark of National Semiconductor Corporation All other trademarks mentioned in this document are property of their respective componies.

# 1.4.1 SX48/52 FUSE Word (Read/Program at 1FFFh in main memory map)

| TURBO      | SYNC                                                                                          | OPTIONX                         | STACKX                                                           | IRC      | DIV2     | DIV1      | DIV0              | CP       | WDTE    | FOSC1 | FOSC0 |  |  |  |

|------------|-----------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------|----------|----------|-----------|-------------------|----------|---------|-------|-------|--|--|--|

| 11         | 10                                                                                            | 9                               | 8                                                                | 7        | 6        | 5         | 4                 | 3        | 2       | 1     | 0     |  |  |  |

|            | Turba mada anabla:                                                                            |                                 |                                                                  |          |          |           |                   |          |         |       |       |  |  |  |

| TURBO      | Turbo mode enable:<br>0 = turbo mode (instruction clock = osc/1)                              |                                 |                                                                  |          |          |           |                   |          |         |       |       |  |  |  |

|            | 0                                                                                             |                                 | •                                                                |          |          | ,         |                   |          |         |       |       |  |  |  |

| 0)(1)(0)   | 1 = compatible mode (instruction clock = osc/4)<br>Synchronous input enable (for turbo mode): |                                 |                                                                  |          |          |           |                   |          |         |       |       |  |  |  |

| SYNC       |                                                                                               | •                               |                                                                  | r turdo  | mode):   |           |                   |          |         |       |       |  |  |  |

|            | 0 = enabled<br>1 = disabled                                                                   |                                 |                                                                  |          |          |           |                   |          |         |       |       |  |  |  |

|            |                                                                                               |                                 |                                                                  | abla     |          |           |                   |          |         |       |       |  |  |  |

| OFTIONA    | 0                                                                                             | PTION register                  | V register inc                                                   |          | from six | to olab   | bite for          |          | and PTW | IE    |       |  |  |  |

|            | 1                                                                                             |                                 | l register inc                                                   |          |          | -         |                   |          |         | _IC   |       |  |  |  |

| STACKX     |                                                                                               | ack extension e                 | -                                                                |          |          | st signin |                   |          | 101)    |       |       |  |  |  |

|            | 0                                                                                             |                                 | 8 levels (stack extension enabled)                               |          |          |           |                   |          |         |       |       |  |  |  |

|            | 1                                                                                             |                                 | ·                                                                |          | ,        |           |                   |          |         |       |       |  |  |  |

| IRC        | In                                                                                            |                                 | 2 levels (stack extension disabled)<br>nal RC oscillator enable: |          |          |           |                   |          |         |       |       |  |  |  |

|            | 0                                                                                             | enabled                         | - OSC1 wea                                                       | akly pul | led low, | OSC2 v    | veakly p          | ulled hi | igh     |       |       |  |  |  |

|            | 1                                                                                             | = disabled                      | I - OSC1 and                                                     | OSC2     | behave   | accordi   | ng to FC          | DSC1:    | FOSC0   |       |       |  |  |  |

| DIV2: DIV0 | ) In                                                                                          | Internal RC oscillator divider: |                                                                  |          |          |           |                   |          |         |       |       |  |  |  |

|            | 00                                                                                            | 00b =                           | 4 MH                                                             | z        |          |           |                   |          |         |       |       |  |  |  |

|            | 00                                                                                            | )1b =                           | 2 MH                                                             | Z        |          |           |                   |          |         |       |       |  |  |  |

|            | 01                                                                                            | 0b =                            | 1 MH                                                             | z        |          |           |                   |          |         |       |       |  |  |  |

|            | 01                                                                                            | 1b =                            | 500 K                                                            | Ήz       |          |           |                   |          |         |       |       |  |  |  |

|            | 10                                                                                            | 00b =                           | 250 K                                                            | Hz       |          |           |                   |          |         |       |       |  |  |  |

|            |                                                                                               | )1b =                           | 125 k                                                            |          |          |           |                   |          |         |       |       |  |  |  |

|            |                                                                                               | 0b =                            | 62.5 I                                                           |          |          |           |                   |          |         |       |       |  |  |  |

|            |                                                                                               | 1b =                            | 31.25                                                            | KHz      |          |           |                   |          |         |       |       |  |  |  |

| CP         |                                                                                               | ode protect ena                 |                                                                  |          |          |           |                   |          |         |       |       |  |  |  |

|            | 0                                                                                             |                                 | (FUSE, cod                                                       |          |          |           |                   | -        |         |       |       |  |  |  |

| MOTE       | 1                                                                                             |                                 | I (FUSE, coc                                                     | le, and  | ID mem   | ories ca  | n be rea          | ad norn  | nally)  |       |       |  |  |  |

| WDTE       |                                                                                               | atchdog timer e                 |                                                                  |          |          |           |                   |          |         |       |       |  |  |  |

|            | -                                                                                             | = disabled                      |                                                                  |          |          |           |                   |          |         |       |       |  |  |  |

|            | 1:<br>2800 E                                                                                  |                                 | enabled<br>al oscillator configuration (valid when IRC = 1):     |          |          |           |                   |          |         |       |       |  |  |  |

| FUSC1. FU  |                                                                                               |                                 | -                                                                |          | a when i | RC = 1    | •                 |          |         |       |       |  |  |  |

|            |                                                                                               |                                 | v power crys<br>gh speed cry                                     |          |          |           |                   |          |         |       |       |  |  |  |

|            |                                                                                               |                                 | rmal crystal                                                     | siai     |          |           |                   |          |         |       |       |  |  |  |

|            |                                                                                               |                                 | vork - OSC2                                                      | is nulla | d hiah h |           | k nullun <i>i</i> |          |         | nut)  |       |  |  |  |

|            | 1                                                                                             |                                 | - 030Z                                                           | is pulle | u nign b | y a wea   | r pulup           |          |         | puij  |       |  |  |  |

# 1.4.2 SX48/52 FUSEX Word (Read/Program via Programming Command)

| SLEEPCLK        | WDRT2 : WDRT0                                                                                                                                                                                                                 |                                                             | CF                         | CF IRCTRIM2 : IRCT |               |            | RIM0 Unused |                              |             | BOR0:BOR0  |            |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------|--------------------|---------------|------------|-------------|------------------------------|-------------|------------|------------|

| 11              | 10                                                                                                                                                                                                                            | 9                                                           | 8                          | 7                  | 6             | 5 4        |             | 3                            | 2           | 1          | 0          |

| SLEEPCLK        | Sleep Clock Disable. Clear this bit to 0 to enable operation of the clock during power down mode (to allow fast start-up). Set this bit to 1 to disable clock operation during power down mode (to reduce power consumption). |                                                             |                            |                    |               |            |             |                              |             |            |            |

| WDRT2:<br>WDRT0 | Delay Reset Timer (DRT) timeout period. This 3-bit field can be used to specify the DRT timeout period that results in an automatic wake-up from the power down mode:                                                         |                                                             |                            |                    |               |            |             |                              |             |            |            |

|                 | 100 = 0 $101 = 0.0$ $110 = 7.0$ $111 = 18$ $000 = 60$ $001 = 48$ $010 = 96$ $011 = 19$                                                                                                                                        | 06 mse<br>68 mse<br>8.4 mse<br>0 msec<br>60 msee<br>60 msee | ec<br>ec<br>ec (defau<br>c |                    |               |            |             |                              |             |            |            |

| CF              | to 100. T                                                                                                                                                                                                                     | his will                                                    | keep th                    | e clock o          |               | uring the  | power dow   | CLK bit and s<br>vn mode an  |             |            |            |

| IRCTRIM2:       | Internal F                                                                                                                                                                                                                    | RC Os                                                       | cillator T                 | rim. This          | 3-bit field a | adjusts th | e operatio  | on of the inte               |             |            |            |

| IRCTRIM0        |                                                                                                                                                                                                                               |                                                             |                            |                    |               |            |             | iinus 8%. Pa<br>provide trim |             | oped fron  | n the fac- |

|                 | 000b = n                                                                                                                                                                                                                      | ninimur                                                     | n freque                   | ency               |               |            |             |                              |             |            |            |

|                 | 111b = n                                                                                                                                                                                                                      | naximu                                                      | m frequ                    | ency               |               |            |             |                              |             |            |            |

|                 | each ste                                                                                                                                                                                                                      | p appro                                                     | ox. 3%                     |                    |               |            |             |                              |             |            |            |

| BOR1: BOR0      | Brown-C<br>disabled                                                                                                                                                                                                           |                                                             | et; facto                  | ory preset         | values. Bit   | s should   | not be cha  | anged unles                  | ss brown-ou | ut feature | is to be   |

|                 | 00b = br                                                                                                                                                                                                                      | own-ou                                                      | it enable                  | ed                 |               |            |             |                              |             |            |            |

|                 | 01b = (re                                                                                                                                                                                                                     | eserved                                                     | l)                         |                    |               |            |             |                              |             |            |            |

|                 | 10b = (re                                                                                                                                                                                                                     | eserved                                                     | I)                         |                    |               |            |             |                              |             |            |            |

11b = brown-out disabled

# 1.4.3 FUSE/FUSEX changes

There are some additional features which will be made available in the production released revision of SX48/52, including a change to the arrangement of the FUSE and FUSEX bit assignments. Please see section 3.0 for more details on these improvements.

# 1.5 Data Memory

The data memory is a RAM-based register set consisting of 262 general-purpose registers and nine special-purpose registers. All of these registers are eight bits wide.

The data memory is organized into 16 banks, designated Bank 0 through Bank F, each containing 16 registers, plus an additional bank of 16 "global" registers. Because the registers are organized into banks or "files," these memory-mapped registers are called "file registers."

# 1.5.1 Addressing Modes

Each SX instruction that accesses a data memory register contains a 5-bit field in the instruction opcode that specifies the register to be accessed. The abbreviation "fr" represents the 5-bit register address designator. For example, the instruction description "mov fr,W" means that a 5-bit value or label must be substituted for "fr" in the instruction, such as "mov \$0F,W" (to move the contents of the working register W into file register 0Fh).

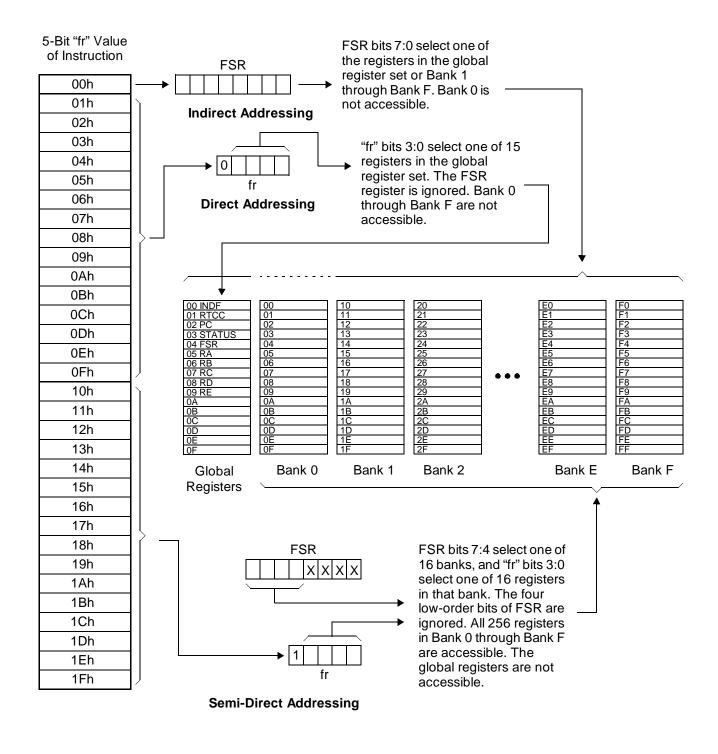

There are three different addressing modes, called the indirect, direct, and semi-direct modes. The addressing mode used for register access depends on the 5-bit "fr" value used in the instruction:

- indirect mode: fr = 00h

- direct mode: fr = 01h through 0Fh

- semi-direct mode: fr = 10h through 1Fh

For indirect addressing (fr=00), the File Select Register (FSR) specifies the register to be accessed. FSR is an 8bit, memory-mapped register (at address 04h) which serves as an 8-bit pointer into data memory for indirect addressing. In this mode, the global register bank and Bank 1 through Bank F are accessible. Bank 0 is not accessible.

For direct addressing (fr=01-0F), the value of "fr" itself specifies the register to be accessed, and the FSR regis-

ter is ignored. For this addressing mode, only the global register bank is accessible. To gain access to any other bank, you must use either indirect or semi-direct addressing.

For semi-direct addressing (fr=10-1F), the bank number is selected by the four high-order bits of FSR, and the register within that bank is selected by the four low-order bits of "fr." In other words, the register address is obtained by combining the four high-order bits of FSR with the four low-order bits of "fr". In this addressing mode, the low-order bits of FSR are ignored. Bank 0 through Bank F are accessible, but the global register bank is not accessible.

Figure 1-1 shows how register addressing works in the indirect, direct, and semi-direct modes. The 16 global registers are always accessible by direct addressing, regardless of what is contained in the FSR register. The global registers are also accessible with indirect addressing, but they are not accessible with semi-direct addressing. Of the 16 global registers, nine are special-purpose registers (RTCC, PC, STATUS, and so on), and six are general-purpose registers. Location 00 is used for indirect addressing (INDF). All of the registers in Bank 0 though Bank F are general-purpose registers.

#### 1.5.2 SFRs and Globals

The SX48/52 have all the same special-function registers as the SX18/28 devices. The SX48/52 however, feature two additional I/O ports, RD and RE, which correspond to addresses \$08 and \$09 respectively. For this reason, user-assignable global memory starts from address \$0A, instead of \$08 on the SX18/28. Therefore, there are only 6 user-assignable global data memory locations available instead of the 8 locations available on SX18/28 some code may need to be rewritten to limit the use of global memory locations.

#### 1.5.3 BANK switching

In order to access data memory locations across other banks, the upper 4-bits of the FSR serve as a pointer to the currebt bank being accessed. To change the contents of the FSR register, the program can either write an eight-bit value to the FSR register or use the "bank" instruction. The BANK instruction writes the three highorder bits in the FSR register, and clears bit 4 of the FSR. Thus, the BANK instruction alone,

bank \$20

lets you quickly change from one even-numbered bank to another (banks \$00, \$20, \$40, \$60, \$80, \$A0, \$C0, \$D0 and \$F0). To change from one odd-numbered bank to another, FSR bit 4 must be set immediately following the BANK instruction as below.

bank \$10 sb FSR.4 Carefull consideration must always be paid to the correct handling of bit 4 in the FSR to ensure that you are pointing to the correct data memory bank.

Note: The BANK instruction will be modified in the production released revision of SX48/52 to help alleviate some of difficulty surrounding bank switching. Please see section 3.0 for more details on these improvements.

# 1.5.4 BANK 0 Considerations

BANK 0 (data memory address \$00 - \$0F) shares the same physical addresses as the SFR registers so deserves special attention. BANK 0 can only be accessed via semi-direct addressing, where bit 4 of the operand address must be set, so the operand address created on assembly should be in the range \$10 - \$1F. The upper 4-bits of the FSR would also need to be cleared.

Since BANK 0 cannot be accessed via direct or indirect addressing modes, some tool vendors may choose not to support this register bank in debug mode. Please consult your tool vendors documentation for more information on this limitation.

Figure 1-1. Register Access Modes

# 2.0 SX48/52 ADDITIONAL FEATURES

There are several new features specific to the SX48/52 that were not available in previous members of the SX family.

# 2.0.1 Multi-Function Timers

Two additional 16-bit timers with 8-bit prescalers with the following operating modes have been implemented:

- Software Timer mode

- PWM mode

- Simultaneous PWM/Capture mode

- External Event mode

Please consult the SX48/52 datasheet for more details on all the SX48/52 features.

#### 2.0.2 Interrupt Sources

In addition to the internal Real-Time Clock/Counter (RTCC) interrupt and the external PORT B interrupts, timers T1 and T2 each has three interrupt sources associated with counter overflow, compare match, and input capture. As there is still only one interrupt vector, special attantion must be paid to determining the soucre of interrupt at the beginning of the interrupt service routine (ISR) if multiple sources are enabled. The handling of these interrupts may induce jitter in the timing of Virtual Peripheral<sup>TM</sup> modules if the RTCC interrupt is enabled along with other interrupt sources.

An RTCC Overflow Flag bit (RTCCOV) has also been added, and contained in the T1CNTB register. This flag is automatically set to 1 when the RTCC overflows from FFh to 00h. This flag stays set until it is cleared by the software. Note that this flag is not related to multi-function timers T1 and T2.

#### 2.0.3 PORT Read Feature

Reading from a data register reads either the voltage levels of the corresponding port pins or the data contained in the port data register depending on the status POR-TRD bit contained in the T2CNTB register.

# 2.0.4 Delay Reset Timer (DRT)

The FUSEX register contains this 3-bit field which can be used to specify the DRT timeout period that results in an automatic wake-up from the power down mode. Timeout periods of 0, 0.06, 7.68, 18.4, 60, 480, 960 or 1920 msec can be selected.

Note:The DRT timeout period is based on the internal watchdog oscillator clock, so these timeout periods are fixed regardless of the external oscillator clock speed.

# 2.0.5 Sleep Clock Disable

This FUSEX bit allows the ability to enable the operation of the clock during power down mode to allow fast startup. Set this bit to 1 to disable clock operation during power down mode (to reduce power consumption).

# 3.0 SX48/52 PRODUCTION RELEASE

The production release of SX48/52 will have some features modified either for compatibility with existing SX18/28 devices or as enhancements.

These include:

- Modification of FUSE and FUSEX bit arrangement and features for maximum compatibility with existing SX18/28 devices or enhanced features

- Removal of PIC 'compatible' features:

- fixed 1:1 instruction:clock ratio

- fixed 8-level stack

- full 8-bit OPTION register

- Same OSC circuitry and settings as existing SX18/28

devices

- Selectable BOR threshold

- Modification of DRT timeout period setting for compatibility with existing SX18/28 devices

- Improved BANK instruction operation

# 3.0.1 SX48/52 FUSE Word (Read/Program at 1FFFh in main memory map)

| Unused   | SYNC  | Unuse                                                                  | d IRC/XTL                                                                                    | DIV1/IFBD     | DIV0/FOSC2                         | XTLBUF_EN       | CP     | WDTE        | FOSC1        | FOSC0  |  |  |  |  |

|----------|-------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------|------------------------------------|-----------------|--------|-------------|--------------|--------|--|--|--|--|

| 11       | 10    | 98                                                                     | 7                                                                                            | 6             | 5                                  | 4               | 3      | 2           | 1            | 0      |  |  |  |  |

| SYNC     |       | Synchr                                                                 | onous outo                                                                                   | ut enable (or | utout transition                   | only on clock   | edae)  |             |              |        |  |  |  |  |

| •••••    |       | 0 =                                                                    | hronous output enable (output transition only on clock edge)<br>enabled                      |               |                                    |                 |        |             |              |        |  |  |  |  |

|          |       | 1 =                                                                    | disabled                                                                                     |               |                                    |                 |        |             |              |        |  |  |  |  |

| IRC      | IRC   |                                                                        | Internal RC oscillator enable                                                                |               |                                    |                 |        |             |              |        |  |  |  |  |

|          |       | 0 =                                                                    | enabled -                                                                                    | OSC1 weal     | kly pulled low,                    | OSC2 weakly     | pulled | high        |              |        |  |  |  |  |

|          |       | 1 =                                                                    | disabled ·                                                                                   | - OSC1 and    | OSC2 behave                        | according to F  | FOSC2  | EFOSC0      |              |        |  |  |  |  |

| DIV1:DIV | /0    | Internal RC oscillator divider                                         |                                                                                              |               |                                    |                 |        |             |              |        |  |  |  |  |

|          |       | 00b =                                                                  | 00b = 4 MHz                                                                                  |               |                                    |                 |        |             |              |        |  |  |  |  |

|          |       | 01b =                                                                  | 1 MHz                                                                                        |               |                                    |                 |        |             |              |        |  |  |  |  |

|          |       | 10b =                                                                  | 128 KHz                                                                                      |               |                                    |                 |        |             |              |        |  |  |  |  |

|          |       | 11b =                                                                  | 32 KHz                                                                                       |               |                                    |                 |        |             |              |        |  |  |  |  |

| IFBD     |       | Internal crystal/resonator oscillator feedback resistor                |                                                                                              |               |                                    |                 |        |             |              |        |  |  |  |  |

|          |       | 0 =                                                                    |                                                                                              |               | •                                  | xternal feedba  |        | uired for c | rystal opera | ation) |  |  |  |  |

|          |       | 1 =                                                                    |                                                                                              |               | ,                                  | valid when IRC  | ,      |             |              |        |  |  |  |  |

| XTLBUF   | _EN   | Crystal Buffer enable (disable when not using a crystal to reduce ldd) |                                                                                              |               |                                    |                 |        |             |              |        |  |  |  |  |

|          |       | 0 =                                                                    | •                                                                                            | uffer enabled |                                    |                 |        |             |              |        |  |  |  |  |

|          |       | 1 =                                                                    | ,                                                                                            |               |                                    |                 |        |             |              |        |  |  |  |  |

| CP       |       |                                                                        | Code protect enable<br>0 = enabled (FUSE, code, and ID memories read back as scrambled data) |               |                                    |                 |        |             |              |        |  |  |  |  |

|          |       | 0 =                                                                    |                                                                                              | •             |                                    |                 |        |             | ata)         |        |  |  |  |  |

| WOTE     |       | 1 =                                                                    |                                                                                              |               | e, and ID mem                      | ories can be re | ead no | rmally)     |              |        |  |  |  |  |

| WDTE     |       |                                                                        | log timer er                                                                                 | nable         |                                    |                 |        |             |              |        |  |  |  |  |

|          |       | 0 =                                                                    | disabled                                                                                     |               |                                    |                 |        |             |              |        |  |  |  |  |

| 50000    |       | 1 =                                                                    | enabled                                                                                      | <b>C</b>      |                                    |                 |        |             |              |        |  |  |  |  |

| FOSC2:F  | -0500 |                                                                        |                                                                                              | -             | n (valid when I                    | RC = 1):        |        |             |              |        |  |  |  |  |

|          |       |                                                                        |                                                                                              | v power crys  | . ,                                |                 |        |             |              |        |  |  |  |  |

|          |       |                                                                        |                                                                                              |               | tal (32KHz - 1)                    |                 |        |             |              |        |  |  |  |  |

|          |       |                                                                        |                                                                                              | •             | (32KHz - 10M                       | ,               |        |             |              |        |  |  |  |  |

|          |       |                                                                        |                                                                                              | -             | (1MHz - 24MF<br>/stal (1MHz - 3    | •               |        |             |              |        |  |  |  |  |

|          |       |                                                                        |                                                                                              |               | /stal (1MHz - 3<br>/stal (1MHz - 5 |                 |        |             |              |        |  |  |  |  |

|          |       |                                                                        |                                                                                              |               | /stal (1MHz - 5<br>/stal (1MHz - 5 | ,               |        |             |              |        |  |  |  |  |

|          |       |                                                                        |                                                                                              |               | •                                  | ed high by a we | ≏ak nu | llun(no Cl  |              | tuc)   |  |  |  |  |

|          |       |                                                                        | External                                                                                     |               |                                    |                 | can pu |             |              |        |  |  |  |  |

# 3.0.2 **SX48/52** FUSEX Word (Read/Program via Programming Command)

| IRCTRIM2 SLI | EEPCLK                                                                                                                                                                                 | IRCTRIM1                 | IRCTRIM0        | Unused     | CF       | BOR1     | BOR0     | BORTR1     | BORTR0       | DRT1     | DRT0 |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------|------------|----------|----------|----------|------------|--------------|----------|------|--|

| 11           | 10                                                                                                                                                                                     | 9                        | 8               | 7          | 6        | 5        | 4        | 3          | 2            | 1        | 0    |  |

|              |                                                                                                                                                                                        |                          |                 |            |          |          |          |            |              |          |      |  |

| IRCTRIM2:    |                                                                                                                                                                                        |                          | tor Trim. Th    |            |          |          |          |            |              |          |      |  |

| IRCTRIM0     | it operate within the target frequency range of 4.0 MHz plus or minus 8%. Parts are shipped from the factory untrimmed. The device relies on the programming tool to provide trimming. |                          |                 |            |          |          |          |            |              |          |      |  |

|              | 000b =                                                                                                                                                                                 | 000b = minimum frequency |                 |            |          |          |          |            |              |          |      |  |

|              | 111b =                                                                                                                                                                                 | maximum                  | frequency       |            |          |          |          |            |              |          |      |  |

| SLEEPCLK     | Sleep C                                                                                                                                                                                | Clock Disab              | le.             |            |          |          |          |            |              |          |      |  |

|              | 0 =                                                                                                                                                                                    | enable op                | peration of the | ne clock d | luring   | power d  | lown mc  | de (to all | ow fast star | t-up).   |      |  |

|              | 1 =                                                                                                                                                                                    | disable cl               | ock operatio    | on during  | power    | down n   | node (to | reduce p   | ower cons    | umption) |      |  |

| CF           | Carry F                                                                                                                                                                                | lag ADD/S                | UB enable       |            |          |          |          |            |              |          |      |  |

|              | 0 =                                                                                                                                                                                    | carry bit i              | nput to ADD     | and SUE    | 3 instru | uctions. |          |            |              |          |      |  |

|              | 1 =                                                                                                                                                                                    | ADD and                  | SUB without     | ut carry   |          |          |          |            |              |          |      |  |

| BOR1: BOR0   | Sets the                                                                                                                                                                               | e Brown Ou               | ut Reset thre   | eshold vol | tage     |          |          |            |              |          |      |  |

|              | 00b =                                                                                                                                                                                  | 4.2V                     |                 |            |          |          |          |            |              |          |      |  |

|              | 10b =                                                                                                                                                                                  | 2.6V                     |                 |            |          |          |          |            |              |          |      |  |

|              | 01b =                                                                                                                                                                                  | 2.2V                     |                 |            |          |          |          |            |              |          |      |  |

|              | 11b =                                                                                                                                                                                  | BOR disa                 | abled           |            |          |          |          |            |              |          |      |  |

| BORTR1:      | Brown-                                                                                                                                                                                 | Out trim bit             | s (parts are    | shipped c  | out of f | actory u | Intrimme | ed).       |              |          |      |  |

| BORTR0       |                                                                                                                                                                                        |                          |                 |            |          |          |          |            |              |          |      |  |

|              | 00b =                                                                                                                                                                                  | minimum                  | threshold v     | oltage     |          |          |          |            |              |          |      |  |

|              | 11b =                                                                                                                                                                                  | maximum                  | threshold v     | /oltage    |          |          |          |            |              |          |      |  |

| DRT1:DRT0    | Delay R                                                                                                                                                                                | Reset Timer              | (DRT) time      | out perio  | k        |          |          |            |              |          |      |  |

|              | 10b =                                                                                                                                                                                  | 0.06 mse                 | С               |            |          |          |          |            |              |          |      |  |

|              | 11b =                                                                                                                                                                                  | 18.4 mse                 | С               |            |          |          |          |            |              |          |      |  |

|              | 00b =                                                                                                                                                                                  | 60 msec                  |                 |            |          |          |          |            |              |          |      |  |

|              | 01b =                                                                                                                                                                                  | 960 mseo                 | )               |            |          |          |          |            |              |          |      |  |

|              |                                                                                                                                                                                        |                          |                 |            |          |          |          |            |              |          |      |  |

# 3.0.3 BANK Switching

The BANK instruction will be modified to provide better access to all 16 data memory banks with maximum software efficiency.

In the production release revision of SX48/52, the upper 4-bits of the FSR will still serve as a pointer to the current bank being accessed. The BANK instruction however, will only modify FSR bits 4, 5 and 6, without affecting the other bits in the register. This will break up the data memory banks into upper and lower blocks, with a single BANK instruction allowing you quickly change from one upper bank to another, or from lower bank to another. FSR bit 7 will need to be modified by the user to switch from an upper to a lower bank (or vice-versa). This allows the maximum number of register banks to be available with a single BANK instruction, while using the FSR to indirectly address another block of addresses, as well as a more 'intuitive' data memory arrangement.

# Sales and Tech Support Contact Information

# DEVELOPMENT TOOLS

#### Parallax Inc.

3805 Atherton Road Rocklin, CA 95765 (916) 624-8333 (916) 624-8003 (fax) http://www.parallaxinc.com

# PRODUCT DISTRIBUTION

# EBV Electronics, Inc.

9980 Huennekens Street San Diego, CA 92121 (800) 677-5664 (800) 556-0225 TECHNICAL SUPPORT HOTLINE (619) 677-7950 (fax)

# MANUFACTURERS REPRESENTATIVES

# Ciponic

Room 1608, 16/F Profit Industrial building 1-15 Kwai Fung St. Hong Kong 011-2482-2981 011-852-2419-7874 (fax)

# Com-File

30-1 Singae-Dong Yougsan-Gu Seoul, Korea 011-822-711-2592 011-82-2-711-2593 (fax)

# **Com-Tek Sales**

3502 Shoreline Drive Navarre, MN 55392-0017 (612) 471-7181 (612) 471-7238 (fax)

# Delta III Associates, Inc.

5397 Twin Knolls Road, Suite 13 Columbia, MD 21045 (410) 730-4700 (410) 730-0790 (fax)

#### Dynamic Technical Sales

416 E. State Parkway, Suite 212 Schaumburg, IL 60173 (847) 755-5490 (847) 755-0532 (fax) 553 Industrial Drive, Suite 6 Hartland, WI 53029 (414) 367-1821 (414) 367-1930 (fax) 12801 Stemmons Freeway, Suite 825 Dallas, TX 75234 (972) 484-5711 (972) 484-0634 (fax)

#### Nelco

M-Rep

9725 E. Hampden Avenue, Suite 100 Denver, CO 80231 (303) 671-7677 (303) 671-7994 (fax)

6032 Caprock Court, Apt. 1807 El Paso, TX 79912 (915) 833-7300 (915) 833-7300 (fax)

# **Optima Sales, Inc.**

901 Campisi Way Campbell, CA 95008 (408) 558-0655 (408) 558-0658 (fax)

# Quality Components, Inc.

116 Fayette Street Manlius, NY 13104 (315) 682-8885 (315) 682-2277 (fax)

# Schillinger Associates,

Inc. 2297 E. Boulevard Kokomo, IN 46902 (765) 457-7241 (765) 457-7732 (fax)

# Spectrum Sales

31368 Via Colinas, Suite 101 Westlake Village, CA 91362 (818) 706-2919 (818) 706-2978 (fax)

# STG

101 Washington Street, Suite 6 Huntsville, AL 35801 (205) 534-2376 (205) 534-2384 (fax)

207 New Edition Court Cary, NC 27511 (919) 468-1524 (919) 468-1534 (fax)

6045 Atlantic Boulevard Norcross, GA 30071 (770) 239-7576 (770) 239-7589 (fax)

#### Sumisho Electronic Devices Corp.

1 Kandamitoshirocho Chiyoda-ku, Tokyo, 101 Japan (03) 5282-7225 (03) 5282-7235 (fax)

#### Venture

12503 Bel-Red Road, Suite 101 Bellevue, WA 98005 (425) 454-4594 (425) 454-9003 (fax) VentureWA@aol.com

7165 S.W. Fir Loop, Suite 103 Portland, OR 97223 (503) 624-0617 (503) 620-4682 VentureOR@aol.com

#### VISTAssociates, Inc.

237 Cedar Hill Street Marlbourgh, MA 01752 (508) 481-9277 (508) 460-1869 (fax)

For the latest contact and support information on SX devices, please visit the Scenix Semiconductor website at www.scenix.com. The site contains technical literature, local sales contacts, tech support and many other features.

# Scenix Semiconductor, Inc.

# 3140 De La Cruz Blvd., Suite #200

Santa Clara, CA 95054 (408) 327-8888 http://www.scenix.com